英语原文共 7 页,剩余内容已隐藏,支付完成后下载完整资料

用于A / V监视器和电视接收机的单芯片微型计算机

Hing-YipTong

技术操作

摩托罗拉半导体香港有限公司

摘要

本文介绍了一种新的专用微型计算机(MCU),用于在多标准A / V监视器和电视接收机中提供用户友好的菜单驱动的屏幕显示(OSD)。它内置专用硬件用于输入遥控信号。 为了节省芯片尺寸,屏幕显示采用需要较长CPU时间的单行显示缓冲区。它还提供硬件多主机IC(IIC)*总线接口,以便在生产或现场服务期间实现计算机故障排除。 本文还讨论了下一代TV MCU的高级功能。

1 .介绍

个人电脑和电视游戏在消费市场的普及,鼓励了电视接收机中用户友好的菜单驱动的屏幕显示的应用,以增强人机交互的功能和降低成本。 本文描述了一种独特的单芯片微型计算机,包含一系列功能,即:

*多标准OSD端口。

*多主控IC(IIC)*总线。

* 带有定时器输入捕捉(TCAP)的16位可编程定时器系统作为遥控信号输入。

* 八通道6位数模转换器(DAC)。

* 用于电压频率调谐的14位二进制倍频器(BRM)DAC输出。

* 一个4位模数转换(ADC)。

* 三个8位VO端口(24线)。

* 8k字节ROM和320字节用户RAM。

全部由E-bit,HCMOS技术,CPU核心驱动。电视MCU包含56或64针封装。独特的系统设计不仅适用于传统的电视接收机市场,而且还在调制解调器A / V监视器和电视接收机中有广泛应用。 该系统通过消除机械控制,开关和LED显示屏来降低成本,还考虑了与现有主流4位MCU竞争的限制版本以及最先进的A / V监视器和电视接收器的升级版本。(参考文献8,9,10)

2.结构

新的电视MCU(“7”)的框图如图1所示,并给出了其架构的描述。(参考文献1〜4)

图1.单片电视MCU(T7)框图(56脚)

2.1 OSD单行显示缓冲区体系结构(参考1,2)

目前大多数具有片上OSD或独立型OSD IC在市场上销售的电视机MCU,屏幕刷新技术并不用于提供全屏显示。为了覆盖整个市场的范围,单行OSD显示缓冲结构用于使用屏幕刷新来提供全屏显示的低成本解决方案。为了照顾软件,这种技术在CPU上有时间限制。为了克服时序限制,后面还讨论了更多的行缓冲器架构。采用OSD的单行缓冲区有两个原因:

(a)节省模具尺寸

它需要24 x 10 = 240字节的寄存器,全屏显示18个字符10行。每行额外的6个字节是行控制寄存器。另一方面,与此架构相同的显示器只需要24times;2 = 48字节寄存器。

(b)更有效地利用CPU时间

在传统的TV MCU中,CPU不需要刷新OSD,CPU保持等待模式,直到输入命令唤醒。使用这种架构,CPU必须不断刷新屏幕才能显示两行或更多行。每行由最多为1397usNTSC或1664usPAL的软件刷新。由于CPU只需要400us以下就能将24字节数据串行加载入行缓冲区,CPU可以在休息时间内执行其他任务(1000us)。

2.2单行缓冲区描述

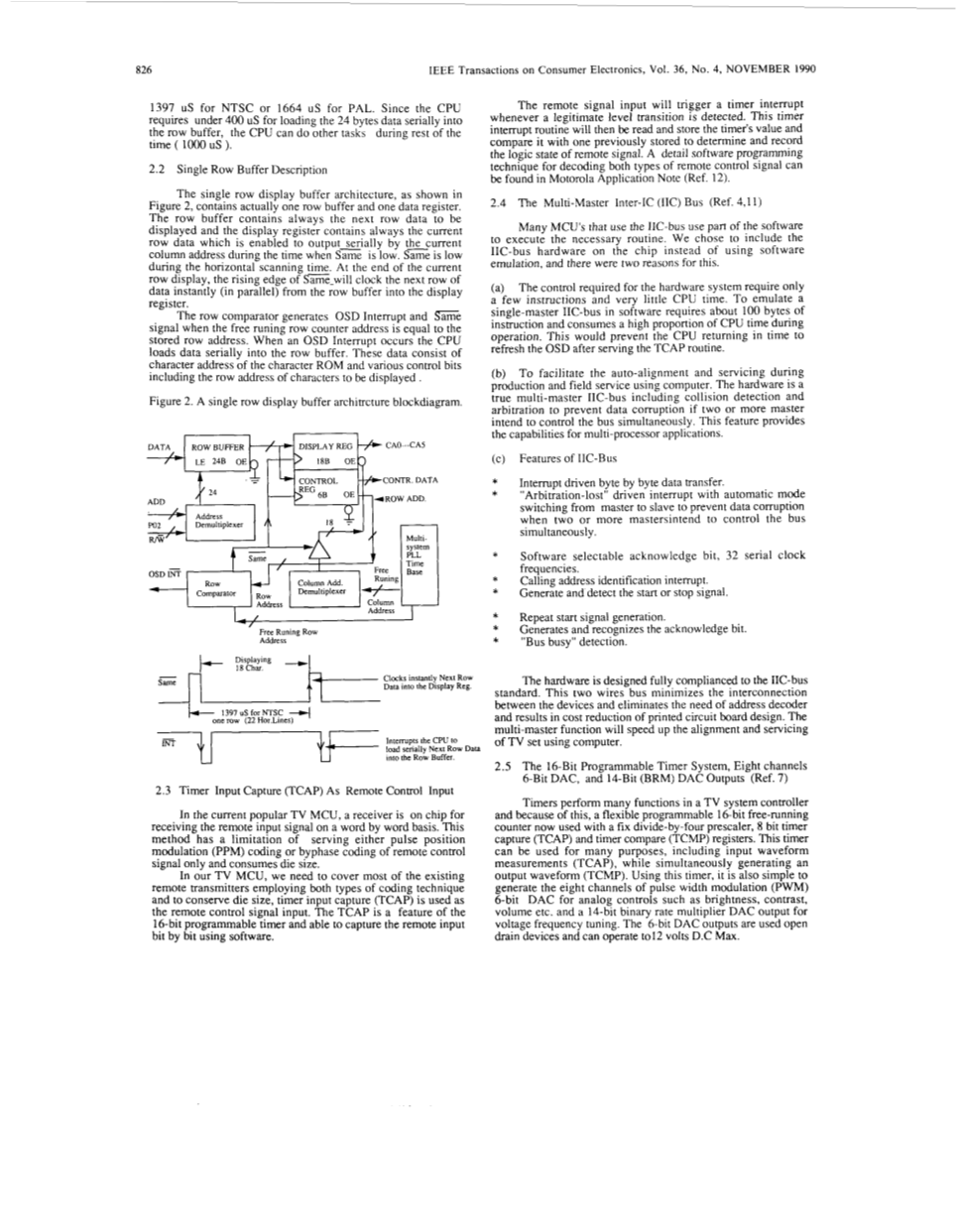

单行显示缓冲区体系结构如图2所示,实际上包含一行缓冲区和一个数据寄存器。行缓冲区总是包含下一行数据并且显示寄存器始终包含当相同值为低时,当前列数据能被串行输出的当前行数据。水平扫描时相同值为低。在当前行显示结束时,相同时钟的上升沿会将下一行数据从行缓冲区立即(并行)输入到显示寄存器中。当自动运行行寄存器地址等于存储的行地址时比较器产生OSD中断和相同信号。当发生OSD中断时,CPU将数据串行加载到行缓冲区中。这些数据包括字符ROM的字符地址和各种控制位,包括要显示的字符的行地址。

图2.单行显示缓冲区构造块图:

2.3定时器输入捕捉(TCAP)作为遥控输入

在当前流行的TV MCU中,接收器是在芯片上逐个接收远程输入信号的。 该方法具有以下限制:要么服务于脉冲位置调制(PPM)编码要么仅对遥控信号进行相位编码,并消耗芯片尺寸。在我们的电视MCU中,我们需要覆盖大多数现有的远程发射机,采用两种类型的编码技术,并节省芯片尺寸,定时器输入捕获(TCAP )用作遥控信号输入。 TCAP是16位可编程定时器的一项功能,可以使用软件逐位捕获远程输入。

当检测到合法的电平转换时,远程信号输入将触发定时器中断。 然后,该定时器中断程序将被读取并存储定时器的值并将其与之前存储的一个进行比较,以确定和记录远程信号的逻辑状态。 在摩托罗拉应用笔记(参考文献12)中可以找到用于解码两种类型的遥控信号的详细软件编程技术。

2.4多主机IC(IIC)总线(参考文献4,11)

许多使用IIC总线的MCU使用部分软件来执行必要的程序。我们选择在芯片上包括IIC总线硬件,而不是使用软件模拟,有两个原因。

(a)硬件系统所需的控制只需要几个指令,CPU时间就很少。以软件模拟单主IIC总线需要大约100字节的指令,并且在操作期间消耗高比例的CPU时间。这将阻止CPU在服务TCAP程序后立即返回刷新OSD。

(b)方便利用电脑在生产和现场服务过程中自动调整和维修。硬件是真正的多主机IIC总线,包括冲突检测和仲裁,能在两个或更多的主机同时控制总线防止数据损坏。此功能提供了多处理器应用程序的功能。

(c)IIC-Bus的特点

*中断驱动逐字节数据传输。

*“仲裁丢失”驱动中断,当两个或多个主控器件同时控制总线时自动从主机切换到从机以防止数据损坏。

*软件可选应答位,32个串行时钟频率。

*产生并检测起始或停止信号。

*呼叫地址识别中断。

*重复启动信号生成。

*生成并识别“Bus busy”检测。 确认位。

硬件设计完全符合IIC总线标准。这种两线总线最小化了器件之间的互连,并且消除了地址解码器的需要,并且导致印刷电路板设计的成本降低。多主机功能可以使用电脑加快电视机的对准和维修。

2.5 16位可编程定时器系统,8个通道

6位DAC和14位(BRM)DAC输出(参考文献7)定时器在电视系统控制器中执行许多功能,因此,灵活的可编程16位自由运行计数器现在与固定分频预分频器,8位定时器捕获(TCAP)和定时器比较(TCMP)寄存器一起使用。该定时器可用于许多目的,包括输入波形测量(TCAP),同时产生输出波形(TCMP)。使用该定时器,也可以简单地生成用于模拟控制(如亮度,对比度,音量等)的8通道脉宽调制(PWM)6位DAC,以及用于电压频率调谐的14位二进制倍增器DAC输出。 6位DAC输出采用开漏设备,可工作在12伏直流电源。

2.6一个4位逐次逼近型模数转换器(ADC)

一个实时时钟和三个8位I / O端口也在图中显示。 4位ADC用于自动频率控制(AFC)的输入,来自视频IF系统的信号以控制调谐器的微调。

2.7 8位脉冲累加器

对于一些数字的TV MCU系列(T4,T9),增加一个脉冲累加器,以在电视台调谐周期中执行信号检测。脉冲累加器是一个8位计数器,可以在以下两种模式之一运行:事件计数模式和门控时间累加器模式。在事件计数模式下,8位计数器通过输入信号计时到增加值。外部事件计数模式的最大时钟速率是E时钟除以2。 E时钟是CPU内核的内部时钟,等于MCU晶体频率除以2。在门控时间累加器模式,仅在外部输入引脚PAIN被激活时自由运行的E时钟产生的信号除以64驱动8位计数器。

2.8模块化设计方法

在系统和IC设计周期中使用模块化设计理念,因为根据特定客户的需求,更容易重新配置系统。 只要允许技术和成本核算,OSD中就有扩展空间来增加更多高级功能,增加了ADC和DAC的通道,增加了I / O,增加了ROM和RAM的大小。

2.9备用Vcc连接提供一个临时的保护,使用户在电源关闭时保留以前的程序数据。

3.下一代电视MCU的高级功能 III

作为系统设计师,我们期待着识别先进的功能,并提升下一代TV MCU的现有性能,以满足未来的市场需求。

3.1添加更多行缓冲区

在最坏的情况下,OSD数据必须每1.4 mS(NTSC)刷新一次,当两行或更多行连续显示时,会发生这种情况。因此,要确保稳定的OSD和顺利运行的MCU控制程序,总共

如(2.1.1)所述,中断程序的执行时间应小于1.4mS或约1.0 mS。有两个条件可能需要添加行缓冲区。

*当全屏显示期间中断程序的总执行时间大于1.0MS时,需要额外的行缓冲器。两行缓冲器为2 mS,三行缓冲区为3 mS ...等

*如果大部分时间,屏幕显示不超过n行,则n行缓冲区通过释放屏幕刷新的时序约束来提供最佳性能,以便CPU有全职工作的其他任务。通常,n取为4或最多5就够了。不幸的是,行缓冲器消耗管芯尺寸并且昂贵,并且成本和性能之间的折衷是非常重要的。

3.2更多缓冲区

未来发展将增加排数缓冲区,为了说明这一点,给出了一个4行架构的例子。

(a)三行缓冲架构

在所示的三行架构中,使用与单行相同的结构,但使用两个添加的缓冲区。 如图3所示,与显示寄存器串联有三个行缓冲器。 添加行缓冲区的关键点是为每个缓冲区生成输出使能OE(1,2,3)和OSD INT(1,2,3)信号,并扩展附加缓冲区的地址解复用器。 三个中断标志(1,2,3)由OSD INT信号设置,通过监视这些标志,CPU能够在适当的点更新每个缓冲区的内容。 然后,该软件将被写入,以在CPU的“安静”期间填充缓冲区。

图3.三行显示缓冲区体系结构框图

(b)四行缓冲器架构

也可以删除显示寄存器并并联连接四行缓冲器,如图4所示。在最坏的情况下,该架构能够连续提供4 mS来处理中断程序。 为每个行缓冲区生成两个相同(1,2,3,4)和OSD INT(1,2,3,4)信号。 有四个中断标志(1,2,3,4)由OSD INT信号设置,通过监视这些标志CPU能够更新每个缓冲区的内容。

图4.四行显示缓冲区体系结构框图

3.3每行增加到24个或更多个字符

现有显示每行18个字符,但是根据需要,每行增加到24个字符甚至更多,因为OSD的架构非常灵活和强大。 显示所需的基本电路修改每行不同的字符数量如表1所示。显然,每行显示的字符越多,时钟频率越高。 幸运的是PLL时基能够调节压控振荡器(VCO)的频率来匹配计数器分频比,确保稳定显示。 (参考文献1,2)

表1

3.4将字符集从64个字符扩展到128个字符(参考文献4)

现有的64字符集不足以满足高端电视和监控市场的需求。 这里需要将字符集增加到128或甚至更多。 我们来看看存储器映射中的一个字符寄存器。

表2.字符寄存器

低6位(bit0到bit5)是字符ROM中的字符地址,它们用于选择64个字符的ROM之一。 位6和位7是字符颜色选择位,用于为包括黑色和白色的八种颜色中的每一行选择四种颜色。通过将字符地址扩展为包含位-6的七位字,可以寻址 一个128个字符集。 这为每排牺牲了两种颜色。 为了保持原来需要8种颜色的每行四种颜色,需要额外的颜色寄存器。

3.5添加颜色寄存器。

需要新的颜色寄存器来将字符集从64个字符扩展到128个字符。 为了节省模具尺寸,我们提出一个颜色寄存器来为两个相邻的字符提供服务。

表3.颜色寄存器

CNO / CN1 ----- N个字符颜色选择位。

两位用于从八种颜色中选择每行四种颜色之一。

C NE -----数字N字符的使能位。

C(N 1)0 / ----- 与CNO / C N1相同的数字

C(N I)1 ------(n 1)个字符。

C(NN 1)E -----数字(N 1)字符的使能位。

共有48个颜色寄存器需要每行24个字符,总共四行。

3.6增加字符分辨率(参考文献1,4)

由于我们现有的设计旨在以低成本优化晶粒尺寸,所以字符点阵在NTSC中为8x11,在PAL中为8x23。 用于字符舍入的半点移位(HDS)由硬件完成。 字符实际上在NTSC中分辨率为16x22,PAL包括16x26,包括HDS。水平和垂直线间距由逻辑零的间距点完成。目前的趋势是增加字符点阵,例如:NTSC中为12x18, 12x22在PAL,并删除HDS硬件,以便任何大小的字符或符号,包括HDS可以通过编程一个或多个字符块构建。

3.7

全文共7838字,剩余内容已隐藏,支付完成后下载完整资料

资料编号:[144698],资料为PDF文档或Word文档,PDF文档可免费转换为Word

以上是毕业论文外文翻译,课题毕业论文、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。