英语原文共 5 页,剩余内容已隐藏,支付完成后下载完整资料

基于FPGA的等精度频率计设计

方一云,陈学军

上海工程技术大学电气与电子工程学院,中国,上海

电子邮件: evafyy@hotmail.com

2012年7月22日受理,2012年8月24日修改,2012年9月3日收稿

摘要:

针对传统频率测量方法不能满足等精度要求的缺点,提出了一种基于FPGA的等精度频率计的设计方法。系统的所有模块都是在Altera公司的FPGA芯片EP2C35F672C8上实现。实验结果表明,本系统可以在整个频率范围内对被测信号频率均实现等精度测量,并且测量误差还很小。该系统达到了等精度测量的要求。

关键词:FPGA; 等精度; 频率测量

1. 介绍

频率测量是电子测量领域中最基本并且最重要的方法之一。频率信号具有抗干扰能力强,易于传输等特点,并且可以实现高精度的测量。因此,对频率测量方法的研究在实际工程应用中具有非常重要意义。目前,最常用的频率测量方法如下,包括直接频率测量法、直接周期测量法以及等精度频率测量法等等方式。直接频率测量法的工作原理是在时间段t内对经过的脉冲信号进行计数,并将计数值记为N,然后计数出每单位时间内经过的脉冲个数,也就是被测脉冲信号的频率。直接周期测量法的测量机理为首先测量出被测脉冲信号的周期T,紧接着再通过公式来计算得到被测信号的频率。然而不足之处是,用这两种测量方法对被测信号进行测量计数时都会产生1个周期的计数误差。因此,直接频率测量法和直接周期测量法在实际工程应用中有着一定的局限性。根据上述两种测量方法的测量原理,可以很容易地得出这样的结论,即直接频率测量法适合用来测高频信号,而直接周期测量法则更适用于频率较低的信号。但是,这两种方法均不能达到同时对高频和低频信号实现等精度测量的要求[1]。等精度频率测量法与其它现有的频率测量方法相比,其最大的优点就是可以在整个测量频率范围内对被测信号均实现等精度测量,并且测量精度不受被测信号频率大小的影响。

2. 等精度频率测量法的原理

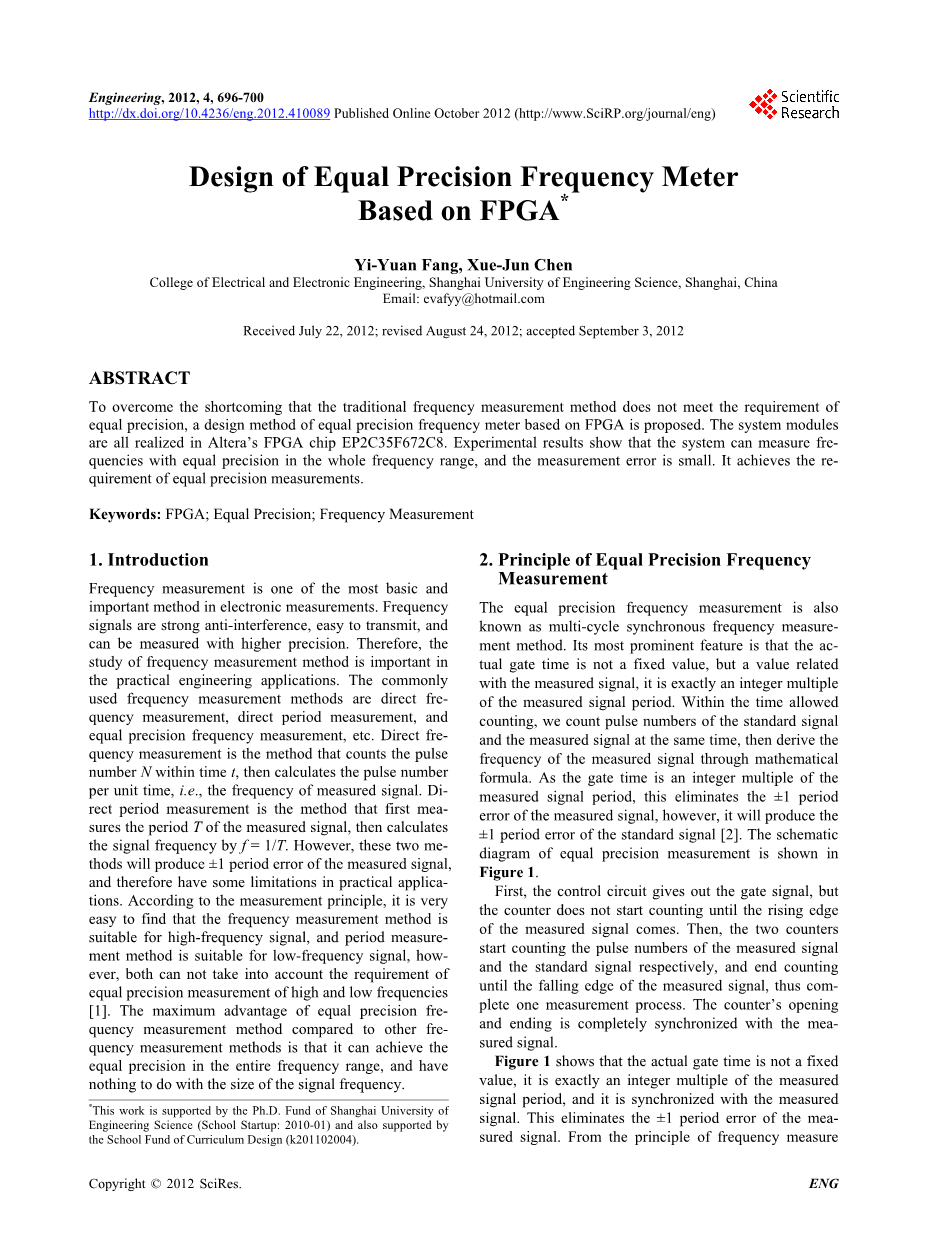

等精度频率测量法又叫做多周期同步测频法,并以此被人们所熟知。等精度频率测量法相比其他方法而言,最为突出的特征是其实际闸门时间并不是一个固定的值,而是一个与被测信号有关联的值,即实际闸门时间正好是被测信号周期的整数倍。在测量允许时间之内,我们对这段时间内经过的被测脉冲信号和标准脉冲信号的个数同时进行计数,然后再根据数学公式求解出被测信号的频率大小。 由于闸门信号的持续时间是被测信号周期的整数倍,所以等精度测频法可以消除对被测脉冲信号计数时产生的个计数误差,但是,该方法将会在对标准脉冲信号进行计数时产生个周期的误差[2]。图1给出了等精度测量的原理图。

首先第一步,控制电路发出闸门信号,但是此时计数器并不会立刻开始计数工作,而是要等到被测脉冲信号上升沿到来的时候才开始计数。随后两个计数器便开始分别对被测脉冲信号个数和标准脉冲信号个数进行计数,其中,两个计数器均直到被测信号下降沿到来的时候才停止计数,由此完成一次测量的全过程。计数器计数工作的开启与关闭是与被测信号完全同步的。

图1 等精度测量原理图

如图1所示,等精度测量原理图表明实际闸门信号的持续时间不是一个固定的值,准确地说闸门时间是被测信号周期的整数倍,并且它与被测信号是同步的。这样便消除了对被测信号计数时的个周期的计数误差。从频率测量的原理,我们不难得出如下结果:

(1)

经过解方程之后,我们可以得到:

(2)

对上述等式两边进行微分,可以得到:

(3)

因为 , ,并且

所以:

(4)

从(4)中我们可以得出这样的结论:等精度测频法的测量误差与被测脉冲信号的频率大小无关,其测量误差仅仅与闸门时间以及标准脉冲信号的频率有关联,也就是说,整个测量频率范围内均实现了等精度测量。当闸门信号的持续时间T 越长,标准时钟信号的频率越高的时候,被测信号频率测量的相对误差也就越小。其中,标准信号频率的相对误差为,又因为晶振有着非常高的稳定性,所以标准信号的相对误差非常小,小到可以忽略不计。

3. 等精度频率计的实现

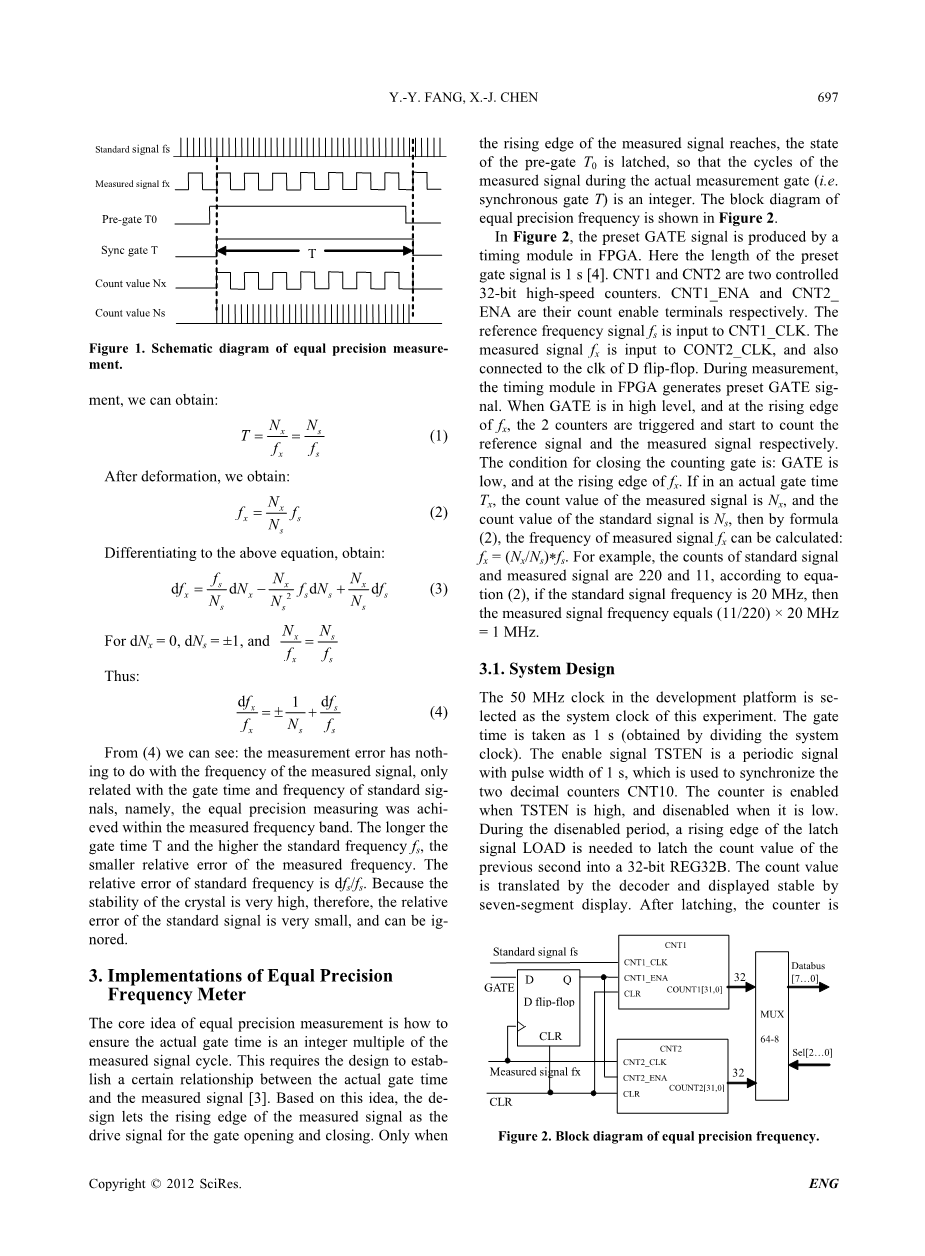

等精度测量方法的核心思想是如何确保实际闸门信号时间是被测脉冲信号周期的整数倍。这样便要求,在设计过程中需要建立起实际闸门信号时间与被测信号二者之间的某个联系[3]。基于这一思想,本设计将被测信号的上升沿作为了闸门开启和关闭的驱动信号。只有当被测信号的上升沿到来的时候,预置闸门的状态才会被锁存,以至于实际测量闸门(也就是同步闸门T)内经过的被测信号的数目是一个整数。图2给出了等精度测频方框图。

如图2所示,等精度测频方框图中的预设闸门信号GATE是由FPGA内部的定时模块所产生的。此处将预设闸门信号的长度设置为1s [4]。CNT1和CNT2是两个受控的32位比特的高速计数器,而CNT1_ENA和CNT2_ENA则分别是计数器CNT1和计数器CNT2的计数使能端。计数器CNT1的时钟输入端CNT1_CLK的输入为参考频率信号,而计数器CONT2的时钟输入端CONT2_CLK的输入信号则是被测信号,并且被测信号还连接到了D触发器的clk输入端。在测量期间,FPGA内部的定时模块产生预设闸门信号GATE。当闸门信号GATE处于高电平时,并且在被测信号的上升沿时刻,此时两个32位的计数器便会被触发,并且开始分别对参考信号和被测信号进行计数。计数器停止计数的条件是:闸门信号GATE处于低电平,同时此刻处于被测信号的上升沿。在实际闸门时间内,如果被测脉冲信号的计数值为,而标准脉冲信号的计数值为,此时便可以通过上文中的数学计算公式(2)将计算出,即被测信号的频率。比如说,当标准脉冲信号的计数值为220,而待测脉冲信号的计数值为11时,根据上述计算等式(2)可知,如果此时标准信号的频率为20 MHz时,那么便可得出被测信号的频率为 (11/220)20 MHz = 1MHz。

3.1 系统设计

开发平台上的50 MHz的时钟被选为当作本设计的系统时钟信号。本设计中,将闸门时间设置为1s(通过将系统时钟分频后获得)。使能信号TSTEN是一个周期信号,并且其脉冲宽度为1s ,其中TSTEN信号的作用是使得两个十进制计数器CNT10能够同步。当使能信号TSTEN处于高电平的时候,计数器便开始工作,而当TSTEN处于低电平的时候计数器便停止计数。在TSTEN处于低电平期间,需要一个锁存信号LOAD的上升沿,来将之前的计数值锁存到一个32位的寄存器中。计数值由相应的译码器进行译码,并且通过七段LED数码管将计数值稳定地显示出来。计数值锁存之后,清零信号CLR_CNT将使计数器中的计数值清零,从而为下一次的计数做好准备。

图2 等精度测频方框图

被测信号的频率计数值是通过8个十进制计数器CNT10的串联而获得,同理可获得标准信号频率的计数值。计数完成后,计数值将被发送至32位寄存器的锁存模块来保存起来。

本研究中,系统开发平台为本设计提供了8个7段LED显示数码管,它最高可以显示到99,999,999。因此,本系统的测量频率范围为0 - 100MHz。其中,显示模块由8个4位二进制代码(BCD码)表示。它将锁存器(32位寄存器)中的数据输出到显示模块,并且通过7段LED数码管显示出这些数据值。使用数据锁存器,是为了确保系统能够稳定地显示数据。译码器驱动电路的作用是将二进制计数结果转换成十进制形式的计数结果,因为十进制形式的结果可以通过7段LED显示出来。

本系统的系统方框图如图3所示。从系统方框图可以看出,系统主要由6个模块组成,它们分别是:源模块、信号选择模块、控制模块、计数模块、锁存模块以及译码显示模块。

3.2 模块设计及功能仿真

3.2.1 源模块

源模块一共包括两个模块,一个是前分频模块,另一个是多分频模块。在本论文中,它们都是通过VHDL语言来编写实现的。前分频模块对系统输入时钟(50 MHz)进行分频,以此来生成1 MHz的时钟频率信号。前分频模块的时序仿真图如图4所示。从图4中我们可以看出,1 MHz的时钟频率是通过将50 MHz的系统时钟经过50倍分频后所得,这实现了本设计预期的理想效果。

图3 系统方框图

图4 前分频模块仿真图

分频器模块CNT具有这样的功能,即它可以产生多种频率的信号。它的主要功能是产生一个脉冲宽度为1 s的闸门信号,一个7812 Hz的扫描信号,以及其它需要的测试信号,这些测试信号包括频率为 500 KHz,、125 KHz、 31250 Hz、 7812 Hz、 1953 Hz、 488Hz和1 Hz的输出信号。输入时钟信号CLK的频率为1 MHz,1 Hz的输出信号freq1被发送至控制模块,此外7812 Hz的输出频率信号被用来作为显示模块的输入扫描信号,而其他的频率信号则作为测试信号。分频器的仿真图如图5所示。

3.2.2 控制模块

在本系统中,控制模块充当的角色是负责产生各种各样的用于测量频率的控制信号。它的输入时钟频率为1Hz,并且每两个时钟周期测量一次频率。输入端CLK连接到分频器CNT的输出freq 1。该控制模块生成3个控制信号,分别为CLR_CNT、TSTEN以及LOAD 信号。CLR_CNT信号负责在每次计数开始的时候对计数器进行复位操作,以此来将上一次的计数结果清除。其中CLR_CNT与计数器CNT10的CLR相连接,为高电平有效,并且持续半个时钟周期。而TSTEN信号则是计数使能信号,连接到计数器CNT10的ENA端。当处于使能信号TSTEN的上升沿时刻,计数器模块便会开始对输入信号的频率进行计数。计数时间是精确的一个时钟周期(也就是单位时间1s),从而这段时间内的计数值便是信号的频率。输出端LOAD与锁存器的输入端LOAD相连。控制模块的仿真图如图6所示。

在仿真图中,控制信号时钟CLK被设置为1Hz,因此TSTEN信号的脉冲宽度正好是1s,其正好可以被用作闸门信号使用。从控制模块仿真图中还可以看出,在计数结束之前使能信号TETEN的高电平持续时间为1s,然后它的反向锁存信号LOAD产生一个上升沿,并且经过0.5s之后清零信号CLR_CNT也产生一个上升沿。

3.2.3 十进制计数器

计数器模块是由8个十进制计数模块CNT10串联在一起而组成的,并且它们带有异步清零和执行信号。该十进制计数器的特别之处在于,它拥有一个时钟使能输入端ENA,其中ENA可以用来将计数器锁住的。当ENA处于高电平时,计数器可以进行计数,而当ENA处于低电平的时候计数器被禁止计数功能。计数器模块的作用是对输入信号的脉冲数目进行计数。该模块必须拥有计数使能端和异步清零端,这样便可以用控制模块对其进行控制。

图5 分频器仿真图

图6 控制模块仿真图

计数器模块CNT10的复位端CLR是与TESTCTL的输出端CLR_CNT连接在一起的,同时CNT10的使能端ENA则是与TESTCTL的TSTEN端相连接,此外CNT10的输出端CQ[3..0]和锁存器的DIN[31..0]端连接在一起。图7给出了CNT10的仿真图。

该模块的功能是实现一个带有使能端的十进制计数器,仅仅当使能信号处于高电平状态时,计数器才能正常工作。每来一个时钟信号的上升沿,计数器中的计数值就会加一。当计数值计到10时,将计数器中现有的值清零,同时产生一个执行信号,其中执行信号仅仅就是一个脉冲信号。一旦计数值从10变为1,该脉冲信号就会立即变为低电平。同时,计数器还有一个清零信号。一旦当清零信号处于高电平状态时,计数器中的计数值将会被立即清零。在本设计中,需要对两个信号进行计数,所以便有两个32位数据的输出端口。

3.2.4 32位锁存器

本系统中,锁存器模块主要是由主从触发器所构成。锁存器在系统中扮演着保护数据的角色,从而保证数据在显示之前的稳定性。在计数模块完成计数工作之后,锁存器模块便会在load下载信号的上升沿时刻将计数值锁存到寄存器中去;然后再输出到显示模块,并且保存数据直至下一次触发信号或复位信号的到来。

锁存器的输入端LOAD与控制模块TESTCTL的输出端LOAD相连,而锁存器的输入端DIN[31..0]与计数器CNT10的输出端CQ[3..0]相连,并且它的输出端DOUT[31..0]是和显示模块的端口In[3..0]连接在一起的。

图7 CNT10仿真图

3.2.5 7段LED显示模块

七段LED数码管有段码和位码,其中段码是用来通过译码电路将4位二进制输入数字转换为供LED显示的相应的8位段码,而位码则是用来使能LED的。对于共阴极LED来说,低电平有效。本设计中使用了一个3位循环选择器,以此来轮流使能每一个LED。因为8个LED需要同时显示,所以我们必须循环扫描每个LED,并且在使能每个LED的同时根据需要显示的数据来输入8位段码。

虽然这8个LED是轮流显示的,但是由于视觉暂留的缘故,实际看上去的效果像是8个LED在同时显示。

显示模块方框图如图8所示。显示模块方框图中的In0 - In7和锁存器的DOUT[31..0]相连,而输出端则是和LED的段引脚以及选择控制引脚连在一起的。

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[26169],资料为PDF文档或Word文档,PDF文档可免费转换为Word

以上是毕业论文外文翻译,课题毕业论文、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。