英语原文共 5 页,剩余内容已隐藏,支付完成后下载完整资料

附录X 译文

基于相变存储器的非易失性“和”、“或”和“非”布尔逻辑门

Y.Li,1,2 Y.P.Zhong,1,2 Y.F.Deng,1,2 Y.X.Zhou,1,2 L.Xu,1,2和X.S.MiaO1,2,a)1华中科技大学武汉光电国家实验室(WNLO),武汉430074,中国光学与电子学院2华中科技大学Ronic Information,武汉430074,中国(2013年11月22日接收,2013年12月6日接收,2013年12月19日在线发布),可以实现逻辑和存储功能的电子设备或电路被视为未来Von Neu以外大规模并行计算的基石。

曼恩建筑。在这里,我们提出了基于相变存储器(PCM)的非易失性逻辑门,能够在SPICE模拟和电路实验中验证和、或(或)非布尔逻辑运算。逻辑操作是并行计算,结果可以直接存储在逻辑门的状态中,便于在同一电路中进行计算和存储器的组合。这些结果对基于新型存储器件的超低功耗高速非易失性逻辑电路的设计具有一定的鼓舞作用。VC 2013 AIP出版有限责任公司[http://dx.doi.org/10.1063/1.4852995]

- 引言

可以存储和处理数据信息的电子设备或电路被认为是新计算架构的基石,以打破冯·诺依曼的瓶颈。1,2相变存储器(PCM)是下一代非易失性存储器替代闪存或用作存储类存储器的一个有前途的坎迪日期,3-5最近已经然而,它通过神经形态和逻辑方法处理信息的惊人能力。6-11在计算机的神经形态范式中,pcm被用作电子突触。利用部分结晶6,7或电荷捕捉8控制的记忆电阻对器件电阻调谐的模拟特性,模拟突触效应的塑性改变。这种模式可能着眼于在长期范围内开发受大脑启发的芯片。就逻辑范式而言,Ovshinsky等人建议12-14和Wright等人利用非晶态相变材料和内置的相变储能器的能量积累效应,进行加、减、因子分解等算术计算。Cassinerio等人通过操作阈值和内存切换行为,演示了单个PCM设备中的布尔逻辑计算。11然而,上述人工逻辑实现仍然存在一些需要解决的缺点。首先,由于晶化过程中的能量积累和阈值切换行为容易受到器件变化和随机形核生长过程的干扰,操作的可靠性或可重复性还远未得到应用。其次,它们都是顺序操作,因为PCM的简单的两端功能。与并行计算相比,虽然占用的设备面积显著减少,但要完成逻辑功能需要多个操作时间较长的步骤,10,11限制了某些超快计算场合的应用。

a)通信地址的作者。电子邮箱:miaoxs@mail.hust.edu.cn。

在这里,我们提出了新的非易失性和,或,而不是逻辑电路组成的PCM器件,电阻和开关。逻辑运算利用了PCM的非晶态和晶态之间的可逆二元切换,简单的相变控制使逻辑运算可靠。这三个简单的电路允许和,或,而不是在一个步骤中实现的三个基本逻辑功能。此外,逻辑计算结果可以直接存储在电路的非易失状态中。通过SPICE仿真和实验结果验证了电路设置和工作原理的正确性。

二丶实验

在SiO2/Si基板上制备了T形PCM器件(TiW 100 nm/Ge2SB2Te5 150 nm/TiW 100 nm)。用紫外锂离子照相法绘制了1 lm2的接触区,并用直流溅射法沉积了薄膜。有关PCM制造工艺的更多详细信息,可在我们之前的工作中找到。8,15 PCM设备通过电线连接到陶瓷封装上,并连接到自行设计的PCB测试板上,以确保电气测量的良好接触。用半导体表征系统(Keithley 4200-SCS)测量了电流-电压(I-V)特性、脉冲开关行为和逻辑运算。使用示波器(安捷伦DSO5012A)获得波形。所有测量均在室温空气中进行。一个紧凑的香料模型的PCM的参考。 我们的模拟采用16,低电阻为10 kx,高电阻为200 kx

三丶结果与讨论

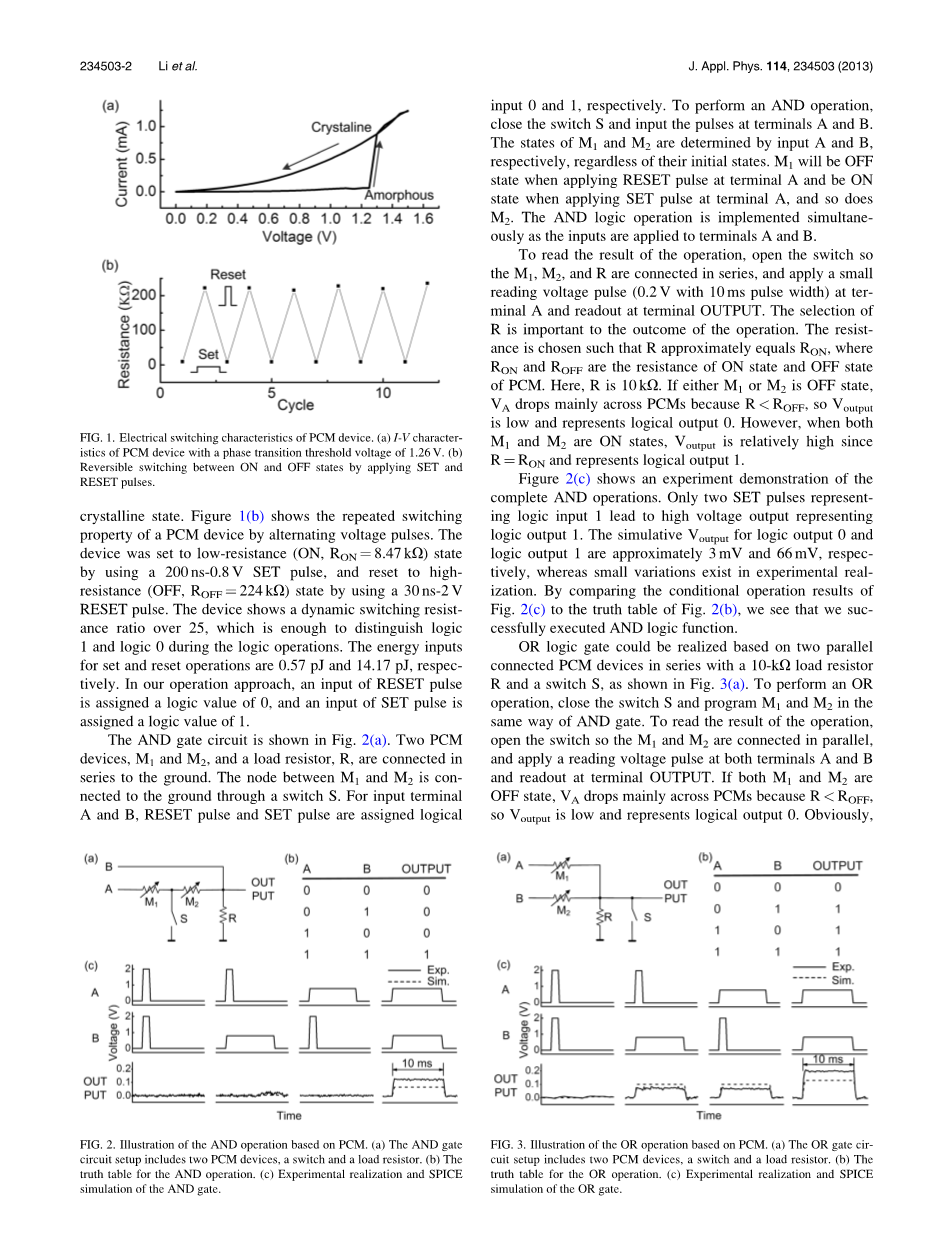

在我们的实验中,PCM的开关作为实现三个基本布尔逻辑函数的基础。图1(a)显示了PCM的实测I-V特性。原始的高电阻器件在1.26V的阈值下切换到低电阻状态,其中Ge2SB2Te5材料经历了从非晶态到非晶态的相变。

图1。PCM装置的电气开关特性。(a)I-V特性-相变阈值电压为1.26 V的PCM装置的特性。(b)通过应用设置和重置脉冲在打开和关闭状态之间可逆切换。

结晶状态。图1(b)显示了通过交流电压脉冲的PCM装置的重复开关特性。装置被设置为低电阻(开,RON 8.47 kx)状态。 通过使用200 ns-0.8 v设置脉冲,并重置为高- 电阻(关闭,ROFF 224 kx)状态,使用30 ns-2 V复位脉冲。该装置显示动态开关电阻- 比值大于25,足以在逻辑运算中区分逻辑1和逻辑0。设置和重置操作的能量输入分别为0.57 pj和14.17 pj。在我们的操作方法中,一个复位脉冲的输入被赋予0的逻辑值,一个设定脉冲的输入被赋予1的逻辑值。

与门电路如图2(a)所示。两个PCM装置M1和M2和一个负载电阻R串联接地。M1和M2之间的节点通过开关S连接到接地。对于输入端A和B,重置脉冲和设置脉冲分配为逻辑脉冲。

图2。基于PCM的和操作的图示。(a)和栅极电路设置包括两个PCM装置、一个开关和一个负载电阻。(b)和操作的真值表。(c)和门的实验实现和SPICE模拟。

分别输入0和1。要执行和操作,关闭开关S并在端子A和B处输入脉冲。M1和M2的状态分别由输入A和B确定,而不管其初始状态如何。M1在A端施加复位脉冲时为关状态,在A端施加设定脉冲时为开状态,M2也为关状态。当输入被应用到终端A和B时,和逻辑操作被同时执行。

要读取操作结果,请打开开关,使M1、M2和R串联,并在端子A处施加一个小的读取电压脉冲(0.2 V,脉冲宽度为10 ms),并在端子输出处读取。R的选择对手术的结果很重要。选择抵抗力时,r近似等于ron,其中 RON和ROFF是动力系统控制模块的接通和断开状态的电阻。这里,r是10 kx。如果M1或M2处于关闭状态,VA主要通过PCMS下降,因为Rlt;ROFF,所以VOutput 低,表示逻辑输出0。然而,当两者都 m1和m2为开状态,voutput相对较高,因为r ron,表示逻辑输出1。

图2(c)显示了完成和操作的实验演示。只有两组脉冲代表逻辑输入1,而高电压输出代表逻辑输出1。逻辑输出0和逻辑输出1的模拟输出分别约为3 mV和66 mV,而实验实际中存在微小的变化。通过将图2(c)的条件运算结果与图2(b)的真值表进行比较,我们发现我们成功地执行了逻辑函数。

或者,逻辑门可以基于两个并联的PCM器件,串联一个10 kx负载电阻R和一个开关S,如图3(a)所示。执行或 操作,关闭开关S,按与门相同的方式编程M1和M2。要读取操作结果,请打开开关,使M1和M2并联,并在端子A和B上施加读取电压脉冲。

在终端输出端读出。如果M1和M2都处于关闭状态,VA主要通过PCMS下降,因为Rlt;ROFF,所以VOutput较低,表示逻辑输出0。显然,

图3。基于PCM的或操作说明。(a)或栅极电路设置包括两个PCM装置、一个开关和一个负载电阻。(b)OR操作的真值表。(c)OR门的实验实现和SPICE模拟。

当m1或m2处于打开状态时,voutput相对较高,因为r r on,表示逻辑输出1。图3(c)显示了证明或操作的模拟和测量电压波。

非门设计如图4(a)所示,其中,PCM装置M与负载电阻配合使用。 r.注意,这里的负载电阻为140 kx,与PCM的高电阻状态相当。逻辑操作只在一个步骤中执行:输入集或 在终端A处复位脉冲,然后在终端输入处施加一个读取电压脉冲,读出操作结果。具体来说,当输入逻辑输入1(设定脉冲)时,PCM被操作到RON,当施加读取脉冲时,电压主要通过负载电阻下降,从而输出低电压(模拟中为13.3 mV,实验中为36.5 mV)。相反,由于逻辑输入0(复位脉冲),PCM被操作到ROFF,因此我们可以在代表逻辑输出1的输出处获得相对高电压(模拟中为156 mV,实验中为133 mV)。图4(b)和4(c)显示了非门的逻辑功能表和操作。

在上述方法中,每个PCM设备首先充当一个开关。开关可以很容易地表示两种状态:开和关,这也是晶体管逻辑门设计的物理基础。第二,PCM器件作为存储器,将逻辑输出存储在门电路中,实现具有非易失性的“有状态”逻辑操作。17此外,通过将AND、OR和NOT逻辑门组合在一起,我们可以构造更复杂的逻辑功能,如NAND、NOR和XOR。换句话说,任何可能的真值表的功能逻辑完整性可以在基于PCM的逻辑门的网络作品中重现。

虽然基于PCM的逻辑门在这一阶段不能超过CMOS逻辑门,但有一些方法可以提高PCM设备的性能,使逻辑门更接近实际应用。PCM设备消耗0.

图4。基于PCM的非操作图示。(a)非门电路设置包括一个PCM装置和一个负载电阻。(b)非操作的真值表。(c)非门的实验实现和SPICE仿真。

待机功率和低动态功率,计算速度快。通过材料的改进、器件结构的优化和编程方案的优化,可以进一步降低开关时间和功耗。近年来的研究进展使得在设定和复位过程中,通过应用孵化电场,可以实现500 ps脉冲的超快稳定的开关。18在Sn10Te90/SB2TE3稀释超晶格器件中获得了超低开关功率。电源约为GST设备的1/2550。19请注意,由于在逻辑门中引入了开关,因此应考虑额外的功耗。开关可以是晶体管、二极管、PCMS或其他闩锁。

与单台PCM设备中的顺序运算相比,本工作还需要11台以上的设备来建立逻辑门。然而,只需要一个编程步骤来实现三个基本逻辑功能,并且使用两个稳定的电阻状态,从而在我们的门中实现更快、更可靠的逻辑操作。我们认为,在未来基于PCM的逻辑芯片设计中,有必要对这两种基于PCM的逻辑门结构的不同方法进行完善,以实现速度和芯片面积之间的最佳权衡。

四、结论

总之,我们提出了一种基于PCM的非易失性逻辑门,它能够和,或,而不是布尔逻辑运算。在SPICE仿真和电路实验中对逻辑函数进行了演示。逻辑运算是并行计算,结果可以直接存储在逻辑门的状态中,便于在同一个电路中组合输入和存储器。非易失性逻辑门的实现可以促进未来非易失性中央处理器(CPU)的设计,具有计算速度快、功耗低的特点。

采用锡底电极相变探针存储器实现低能耗数据存储时代

为了满足大数据时代对记录密度的要求,相变探针存储器被广泛认为是最有前景的候选存储器之一。然而,尽管最近取得了一些进展,但由于使用了通常具有较高电阻率的类金刚石碳底电极,因此相变探针存储器的能耗仍然相当高。本文研究了用氮化钛代替类金刚石作为电极材料的可能性。测量了氮化钛薄膜的厚度和随时间变化的电阻率,使其在相同条件下比类金刚石碳膜具有更好的导电性能和稳定性。因此,利用先前设计的相变探针存储器结构,在氮化钛底部电极的基础上,进行了晶体钻头的写入实验,结果表明,用氮化钛作为底部电极,可以实现超高的记录密度,且比用氮化钛作为底部电极的能量消耗要低。采用类金刚石碳电极的相变堆。

一丶引言

毫无疑问,当今世界正处于大数据时代,所有与公民日常生活密切相关的事物都与数据源相连。大数据时代的到来可以归因于社交网络的繁荣,如Facebook、Twitter和Instagram,以及日常服务的数字化。由于大数据时代的到来,全球数字数据总量在过去5年中急剧增长,2013年已超过4.4 zettabytes,预计到2020年将超过44 zettabytes[1]。这确实需要大力提高传统数据存储设备的记录容量。不幸的是,传统的大容量存储设备受到了各自的物理限制,例如硬盘的超顺磁性、光盘的光学衍射和闪存的缩放限制[2]。在这种情况下,新出现的存储设备及时进入存储字段。

与其他并行存储设备相比,相变探针存储器(PCPM)由于具有超高密度、短切换时间、数据保持时间长和低成本等优点,被认为是最有前途的候选存储器之一[3]。PCPM通常使用具有纳米尺寸的导电扫描探针和三层堆叠,所述三层堆叠包括夹有覆盖层和底层的硫系合金(尤其是Ge2SB2Te5)。在记录过程中,通过导电探针尖端向Ge2SB2TE5介质注入写入电流,以将介质加热至结晶温度或熔化温度,然后快速冷却以产生非晶化。读出过程是通过检测高导电结晶态和高电阻非晶态之间感应电流的差异来实现的。由于PCPM具有吸引力的特点,以前对PCPM的写入和读出性能进行了详细的研究,导致出现了各种相变堆栈[3]、[4]、[5]。尽管存在差异,但任何相变堆都一致要求使用一个能保护Ge2sB2te5介质免受氧化和磨损的封顶层和一个用于收集写入电流的底层。除上述功能外,封顶层的导电率和热导率也需要相对较低,以防止电流泄漏和散热。在这种情况下,类金刚石碳(DLC)薄膜似乎是最适合覆盖层的材料,已被世界各地的研究人员广泛采用[3]、[4]、[5]、[6]。与封顶层相比,底层的物理特性受到较少的关注,因为它只用于收集写入电流。然而,由于底层用作电极,因此期望其导电性高于封端层,从而能够降低记录所需电流以及由此产生的能耗。然而,据作者所知,迄今为止,用于PCPM底部电极的唯一材料是DLC,然而,其表现出相对较高的电阻率[7],导致额外的能量消耗。在这种情况下,有必要探索导电率高于DLC的替代材料,以实现低能耗。

二丶实验

除DLC外,氮化钛(TiN)还因其优异的热机械性能、低电阻率和高温下的冶金稳定性而被认为是另一种有前景的涂层材料[8],[9]。如今,锡已经得到了广泛的应用,从装饰工业中的硬涂层和保护涂层到半导体工业中的扩散阻挡层[10]。除上

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[609379],资料为PDF文档或Word文档,PDF文档可免费转换为Word

以上是毕业论文外文翻译,课题毕业论文、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。