英语原文共 17 页,剩余内容已隐藏,支付完成后下载完整资料

一种2-6GHz、具有28.4%PAE、 65nm CMOS工艺、

支持256QAM 的AB类功率放大器

软件无线电和高数据速率通信需要具有高功率附加效率(PAE)的宽带功率放大器(PA)。一个AB类功放,其可以提供具有优于A类的PAE的线性放大,已经在[1]中报道可以实现大于一个倍程频的带宽。然而,AB类操作产生大量的二次谐波电流在晶体管输出端,其幅度高达基波电流的42%在理论[2]中。输出匹配网络,提供最佳负载阻抗只在基波频率,不足以实现良好的功率性能,给具有倍程频带宽的集成AB类功放设计带来巨大挑战。在这项工作中,我们演示了设计在65nm CMOS的2到6GHz(相对带宽115.5%)AB类功放。一个输出基于差分架构的匹配技术,使功放能够实现最大PAE为28.4%和总PAE高于19%,被建议用来给晶体管输出端提供超过一个倍程频带宽的最佳负载匹配,不仅仅在基波上,还在二次谐波上实现。不使用任何预矫正,在2-6GHz,EVM小于-32dB的256QAM信号功放可以输出9.31-11.31dBm的功率。

图2.5.1显示了所提出的功放的原理图。为了设计输出匹配网络,从2GHz到6GHz对基波频率()和输出级的二次谐波频率的最佳负载阻抗()进行模拟。由并联和组成的模型(对于给定的设备27Omega;和0.94pF)与在带宽上表现出良好的一致性用来合成基频的匹配网络。用设置在基频,从图2.5.2中可以看到和PAE在代表性频率为2.4,3.7和5.8GHz处,在二次谐波负载阻抗的模拟轮廓,其中史密斯圆图上的阻抗被归一化为。它表明尽管负载阻抗在基频达到最佳匹配,但在在二次谐波上和PAE可能会改变4.56 / 4.07 / 3.58dB和29.6%/ 26.1%/ 21.1%。考虑到的电纳,二次谐波阻抗的目标面积在史密斯圆图上表示阻抗接近短路,或容性阻抗归一化幅度小于1,这在晶体管输出的电流源参考平面上是所需要的从而实现良好的和PAE。

为了使基频和二次谐波的匹配超过一个倍频程,采用差分结构,使基波电流在晶体管输出端处于差分模式,但二次谐波电流处于共模。通过利用变压器初级绕组内的耦合以及在两种模式下变压器中心抽头的不同运行状况,可以设计出相应的输出匹配网络,它能提供Zopt_1st和Zopt_2nd大于一个倍频程带宽。如图2.5.1所示,由中心抽头分开两半的变压器初级绕组可以看成是两个耦合线圈(,)。它们之间的耦合()导致基波匹配的差分模式的等效电感和二次谐波匹配的共模的电感的产生。对于基波匹配,一种具有最小反射系数的3阶带通匹配网络[3]合成使用2.3GHz和6GHz作为下带和上带边来确保制造后能够覆盖2.4 GHz和5GHz ISM频带。诺顿转换使得具有 = 2.46nH,k = 0.816和n = 0.826的变压器插入到匹配网络中,输出匹配到50Omega;(图2.5.1)。如果变压器中心抽头是交流接地,用来基波匹配的1.49pF(0.94pF 0.55pF)电容在变压器的每个初级端口上将会与并联的(0.41nH)在6.44GHz处产生谐振(二次谐波3.22GHz),降低功率性能3.22GHz左右。为了获得4-12GHz频率范围的的二次谐波的容性阻抗,电感(1.47nH)插在变压器中心抽头和VDD之间,以将并联谐振频率降低到4GHz以下。将12mu;m宽度的导线用于以将其寄生电阻减小到在直流下仅为0.55Omega;。然后将一个 = 0.5pF的电容连接到变压器中心抽头使得电流源参考平面处的二次谐波的阻抗归一化幅值都小于1。如果太大,并联谐振将发生在较高的频率端,应该避免。较大的可以通过变压器初级的多匝结构获得,当基波匹配需要特定的时,减小的值,从而带来用于二次谐波匹配的更大可实现带宽。因为变压器中心抽头作为差分模式中的虚拟接地,和不会影响基波的匹配。图2.5.2表明添加设计的匹配网络后,二次谐波的负载阻抗在宽频率范围内被移动到目标区域。 与此同时,电流源参考平面处的阻抗被移动到接近短路的区域或具有小于1的归一化振幅的电容性区域。

为了支持单端输入,具有相位误差校正技术的有源巴伦 [4]被用作驱动级来执行单-差分转换在功放的输入端。 巴伦的所有晶体管都被设计有相同尺寸和相同偏置电流。在2-6GHz范围内,当提供所需的驱动功率时模拟相位误差保持小于0.5°。有着0.13times;0.13的小面积,巴伦的两级结构增加了驱动器级的增益,并减少产生目标所需驱动功率的输入晶体管尺寸,允许在大带宽内使用70Omega;的单个电阻作为输入匹配。

为了减少AB类功放的AM-PM失真,在输出级使用基于变容二极管的电容补偿。如图2.5.3所示,不同于传统上使用的PMOS晶体管[5],我们发现PMOS变容二极管的电容与共源共栅结构的输入电容更加互补,其受密勒效应和共栅极器件的输入阻抗的影响。具有较大 / 比率的PMOS变容二极管也降低了总体补偿后的电容,这对于级间匹配网络至关重要从而实现大带宽和良好的增益平坦度。 有了该补偿,功放测量在2至6GHz内AM-PM失真lt;plusmn;2°高达以及增益平坦度为plusmn;0.8dB。

该功放被驱动级的1.8V的直流电流59mA和输出级3.3V的23.6mA所偏置。图2.5.4显示了在2-6GHz内,该功放实现了为23.6plusmn;0.8dB, lt;-11.8dB。 对功放进行大信号测量(图2.5.5),得到在2.8GHz处 的峰值为22.4dBm,在2.3GHz时PAE峰值为28.4%。在整个带宽上,和PAE分别保持在高于20.1dBm和19%,并且在17.81〜20.73dBm范围内(比低1.7至2.4dB)。相比那些没有对二次谐波进行专门匹配的功放来说,该功放在宽频率范围内提高了,和PAE,最大分别提高1.9dB,2.0dB和7.5%。 这些最大的改进都是在3.1GHz处观察到,与分析的结果很吻合。

为了验证该功放在带宽上传送调制信号的能力,帧格式为802.11n(64QAM; 20和40MHz带宽)和中心频率从2到6GHz变化的802.11ac(256QAM; 20,40和80MHz带宽)输入信号,由该功放放大而不使用任何预矫正。当64MAM的EVM增加到-28dB且256QAM的增加到-32dB时,输出功率被记录,结果示于图2.5.6和图2.5.7。由于使用的信号发生器的限制,就没有测量具有160MHz带宽的802.11ac格式信号。随着信号带宽增加,输出功率的降低主要是由于由信号发生器提供的输入信号的EVM增大,对于带宽为20MHz和/或40MHz约为-40dB,但对于80MHz约为-36dB。 PA的性能总结在图2.5.7中,表明该功放可以支持需要从2至6GHz进行线性放大的应用。

在相同的过程中制造,该功放及其对应物各自占据一个包括焊盘0.57times;1.57的区域,如图2.5.7中的显微照片所示。

致谢:

作者感谢VIRTUS(EEE学院,NTU)对这项工作的工作和Global Foundries的芯片制造。

一种2级150W 2.2GHz双路LDMOS射频功率放大器的高效率应用

摘要——本文提出了一种双路径150W硅LDMOS 、专为WCDMA设计的2.2GHz2级射频功率放大器。该设备能够以平坦的射频性能处理2倍的UMTS。 在单频信号连续激励下,该功率放大器可以提供功率150W、且有着47%的功率附加效率和29dB线性增益。一种“内包”构造2 x 75W架构的2级紧凑型Doherty放大器也展示了这种独特设计的多功能性。与在150W,AB类功放的参考设计电路中使用该器件相比,在双路径配置中使用该器件,这个Doherty电路在8 dB输出端从P3dB压缩点开始回退,漏极效率提高9-12点。

索引术语——功率放大器,宽带放大器,硅。

Ⅰ.引言

WCDMA基站系统需要具有高输出功率、低失真和高效率的功率放大器。此外,减少PCB布局面积在这竞争激烈的市场中显得至关重要,从而保持放大器成本最小化。超模压塑料封装的高功率LDMOS射频集成电路在已经发展成为给基站放大器系统提供的简单,成本效益,可靠和竞争性强的解决方案。利用这种集成能力,这个开发工作的目标是构建一个采用多引线封装的150W的2级射频功率放大器。本文提出了一种双路径150W两级LDMOS 射频功率放大器以及此设备在2级Doherty架构的演示。

Ⅱ.设计策略和拓扑

为了实现多个参数的高水平性能,需要以下几个部分:

首先,在模拟方面,一种有源部分的电热模型(MET)在设计模拟阶段已被使用。这个模型已经被仔细提取,优化和验证在给定的频率范围内是准确的。小信号,大信号以及多信号表现已在模拟期间检查通过。负载牵引轮廓的阻抗预测也是此模型创建工作的一部分。关于集成无源元件,一种专门用于电磁(EM)仿真的介质定义,允许采集基波和谐波频率下、精确的无源元件的表现性能。 此外,引线接合法的全波模拟,结合模具和包装的相互作用,在设计性能的优化和预测中发挥着重要的作用。

相比以前的HVIC世代,飞思卡尔的HV7IC技术实现了更高的2级增益和效率,主要是由于集成电感和电容器元件的Q值提高。末级的馈送已经被仔细考虑,通过将驱动级分为4块。这允许在输出级的有源模块的馈送中具有更好的相位梯度,并且还减少来自用于创建FET模型的有限器件尺寸的推断误差。

视频带宽(VBW)已经成为现代射频放大器设计的一个非常重要的优点,作为多载波放大器,高带宽信号和数字预失真(DPD)已经普及用于WCDMA系统。在设计阶段,VBW已经被监视以确保级间匹配网络不是此参数的主要限制。

当此设备有接近30dB的增益,并在单个封装中实现,其稳定性已被仔细检查,通常保留用于单级离散设计。在测量过程中,这个参数的良好表现已经被模拟和验证。

在易用性方面,这部分输入和输出达到预匹配,所以外部射频匹配网络就十分简单并且他们的设计直接明确。AB类功放中,集成热跟踪电路保持静态电流在温度上恒定,并且能够进行C类操作。使得这部分完全兼容Doherty操作。

最后但同样重要的是,由于多引线封装,两个75W独立的2级阵容已经被设计并可以用于双路径模式。每个75W的拓扑结构如图1所示。

Ⅲ.射频性能

- 负载牵引数据

脉冲CW负载牵引已被运用在在一条75W路径上,利用具有无源调谐器的Maury系统,脉冲宽度设置为9 us,占空比为10%。

表1显示了在P1dB和在最大输出功率位置处、2.08~2.2GHz 之间的脉冲负载牵引数据。该集成电路偏置在28V Vd,120mA的1级静态电流(Idq1)和700mA的2级静态电流(Idq2)。这些结果表明,在2倍的UMTS频带内,性能平坦度是良好的。 此外,输出阻抗在频率上的低传播促成了宽带输出匹配到50Omega;。

- 连续单信号性能

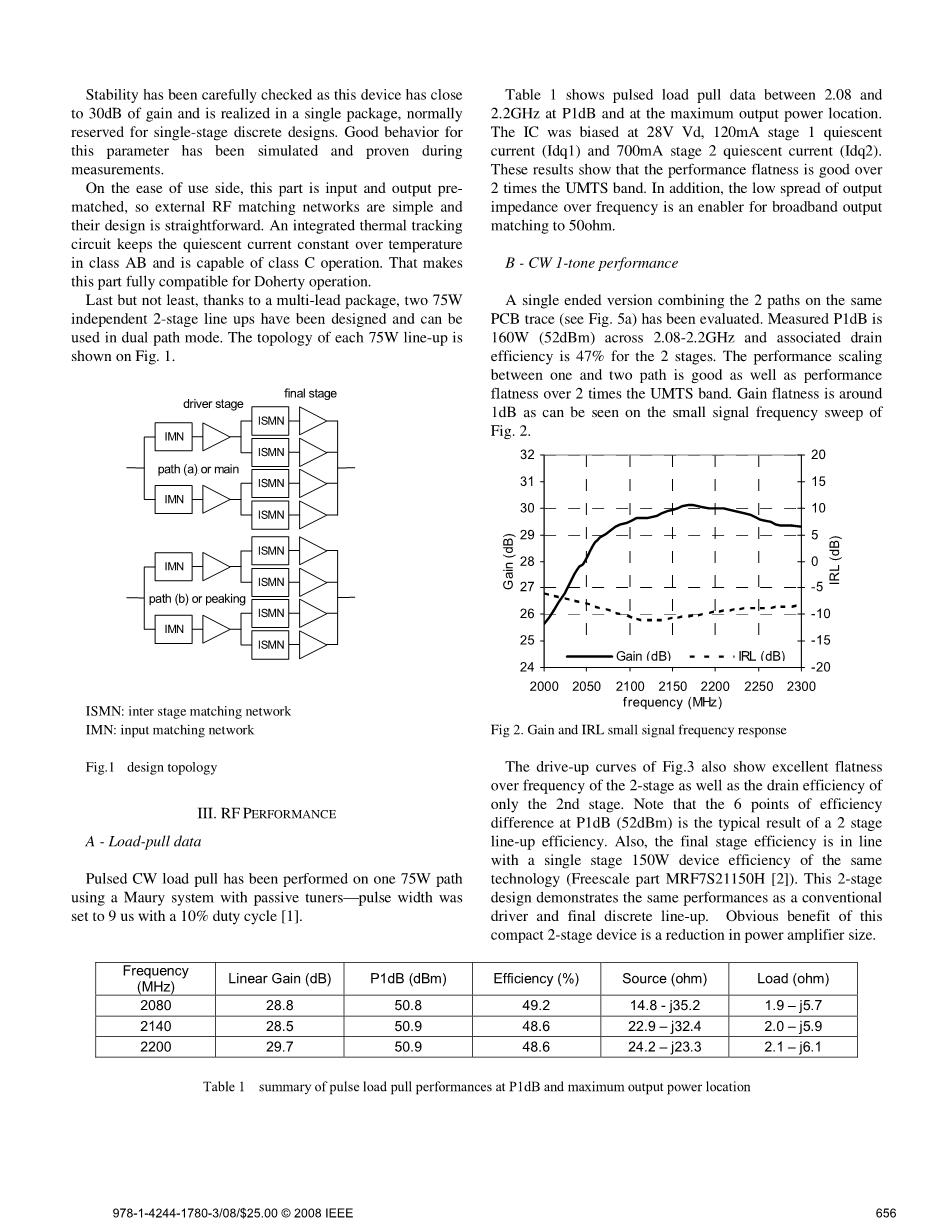

一个单端版本结合的在相同PCB轨迹上(见图5a)的两个路径已经被评估。 在2.08-2.2GHz范围内测量P1dB为160W(52dBm)以及两级的相关漏极效率为47%。在一个和两个路径之间的性能缩放以及在2倍UMTS频带内的性能平坦度都是良好的。增益平坦度接近1dB,可以从图2的小信号频率扫描中看出。

图3的驱动曲线也显示出在2级频率内优异的平坦度以及只在第二级的漏极效率。注意在P1dB(52dBm)处6点的效率差是2级阵容效率的典型结果。 此外,最终级的效率与采用相同技术(飞思卡尔部分MRF7S21150H)的单级150W器件的效率值一致。这个2级设计表现出与常规驱动器和最终离散阵容相同的性能。这个紧凑型2级器件的显而易见的好处是功率放大器尺寸的减少。

- 视频带宽

如前所述,VBW对于应用在DPD系统的设备是至关重要的。在集成电路设计阶段已特别注意到这一参数。集成偏置线长度和损耗,以及去耦电容值已被优化。VBW已经在一个75W器件上用一种双频连续波信号进行测试。中心频率设置为2.14GHz,在75W PEP处,频调分离在1MHz到100MHz范围内已经被改变。如图4所示,IM3-Up和IM3-Low不平衡度小于2dB,直到最终级漏极馈电电路在60MHz出现第一次谐振。这个结果与75W单级LDMOS分立晶体管结果一致。

与单端设备相比,双路径设备允许多个配置。单端(a),双路径(b),平衡或推挽式(c)和Doherty(d)可能的布局,如图5所示。

- (b)

(c) (d)

图5 双路径设备的可能布局

对于高效率应用,Doherty布局被验证能够提高回退效率。由于驱动级的集成,一个紧凑型2级Doherty电路已被设计。输入分离器是3dB威尔金森,输出组合器是一个45欧姆的印刷四分之一波长微带线。一条75W路径用作Doherty主放大器,而第二路径是峰值Doherty放大器。峰值放大器的驱动器和最终级在C类中偏置。Doherty放大器的图像如图6所示。

图6 2x75W Doherty评估板的图片

A.小信号数据

增益和输入回波损耗的小信号响应频率如图7所示。注意,与AB类结果相比的3dB增益差异是Wilkinson输入分路器的典型结果。

B.单频连续波数据

图8和图9显示了增益和效率驱动曲线。在45.5dBm处,或从脉冲饱和功率8dB输出回退处,效率为33%(4.5V)。这是一个9个dB点的改进相比于图4显示的AB类效率。通过减小峰值偏置电压,增加3个效率点可以被获得以电源驱动的增益为代价。

这种紧凑的2级Doherty的一个明显的优点是功率放大器尺寸减小,消除了对于离散驱动晶体管的需求和相关成本的改进。

Ⅴ.结论

双路150W硅LDMOS 2级RF功率放大器的实现已经提出。在UMTS频带中,此功率放大器可提供功率150W,且有着47%的功率附加效率和29dB线性增益。一种两级紧

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[140343],资料为PDF文档或Word文档,PDF文档可免费转换为Word

以上是毕业论文外文翻译,课题毕业论文、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。