英语原文共 12 页,剩余内容已隐藏,支付完成后下载完整资料

高性能多位△sum;CMOS ADC

Yves Geerts, Student Member, IEEE, Michel S. J. Steyaert, Senior Member, IEEE, and Willy Sansen

摘要:提出多比特△sum;转化器的设计。用3阶4位的结构,在反馈环路中为减小数模转化的非线性影响加入了数据加权平均(DWA)算法。由于时钟频率达到100MHz,在反馈环路中为减小DWA带来的延迟,对DWA的延迟进行了最优化。

利用行为模型决定各个模块的参数。利用精确的模型分析跨导运放的闭环主极点、开关的非零电阻及转换速率带来的影响。在量化器中偏置的设置导致量化器有较大的输入电容。因此在经典的单比特sum;△转化器中对OTA的缩放不再使用。

在过采样率仅仅24的条件下,转换器达到了95dB的信噪比,信噪失真比达到89dB,经过梳状滤波器后输入动态范围为97dB。转换器在60MHz采样,有2.5MS/s输出率。转化器采用0.65mu;m的CMOS标准工艺制作,芯片面积5.3,在5V供电电压下的功耗为295mW。当采样率是8,时钟频率是100MHz,输出率为12.5MS/s时,能达到12-bit的精度。

关键词:模数转换,CMOS集成电路,sigma-delta调制器,开关电容电路

Ⅰ.介绍

在传统的通信接收器中,模拟前端通道选择的实现需要更多滤波和更大的增益。这种接收器在模数转化器(ADC)的动态范围和带宽方面的实施比较容易,由于接收器仅仅需要数字化一个通道和大多数的模块信号用模拟前端进行滤波。这种方法常常用在手机。

在宽带接收机中使用不同的方法,其模拟前端中的通道选择的增益和滤波被最小化。全通道的ADC转换器同时用于数字域,所以通道选择和滤波得以实现。这种类型的接收器被用于基站,因为仅仅一个接收器能同时完成所以通道的编码。自然这中接收器需要高精度和大宽带的ADC,因为大量的模块信号出现和许多通道需要同时转换。

宽带网的需求超过了双绞线,这是驱动高性能ADCs发展的动力。在数字用户线系统中,例如ADSL,输入信号1.1MHz,包含离散多音(DMT)信号,需要被转换到数字域。复杂的解码在数字域通过傅里叶变化实现。接收器的结构决定了ADC的精度是12到16位。通常,流水线和Sigma-Delta ADC应用于其中。流水线转换器需要一些校正或误差校正技术达到12位或更高,这样会导致复杂度的提高。另一方面对Sigma-Delta转化器来说,是很适合到达16位及以上的精度。由于过采样,抗混叠滤波器的设计比流水线的设计更容易。通常过采样率在2或4倍可以减少对抗混叠滤波器的要求。因此具有低过采样率的Sigma-Delta转化器非常适用于高性能ADCs。

本论文的安排如下,第二部分选择拓扑,第三部分考虑在Sigma-Delta调制器中的非理想因素。关于不同模块的设计问题在第四部分讨论,第五部分关于测试的结果,最后在第六部分提出一些结论。

Ⅱ.系统级设计

- 拓扑选择

为了结合高速度和高精度,应该选择较低的采样速率,这样可以限制转换器的时钟频率,从而满足积分器的带宽要求。

传统的单环单比特△sum;转换器,在低采样率的条件下实现高精度需要较高的阶数。然而,阶数的提高导致稳定性的严重下降,最后导致SNR严重的下降,与理想的n阶结构相比[5],[6]。

级联拓扑结构[7],[8]能达到高阶噪声整形且具有二阶转换器的稳定性。这种结果的主要缺点是需要较好的模块设计,为防止第一级泄露到输出级的噪声。

最后,多位量化器能使转化器性能有很大的提升。此外,量化器的位数每增加一位,SNR提高6dB,同时稳定性得到提高。这样能达到更高噪声整形,从而精度得到提高[5],[6],[9]。

图1 多位△sum;数据转换器的系统框图

多位量化器的主要问题是DAC的线性问题。由于DAC处于反馈环路中,其精度至少需要达到△sum;转换器的精度,保证不恶化总体性能。几种解决DAC线性问题的方法已经提出[5]。

双量化技术[10],[11]利用单位反馈到第一级,利用多位反馈到最后一级。大大降低了对线性的要求。然而,由于不是所有的级都用多位量化,不严格的噪声整形函数的必须应用,导致性能损失。除此之外,双量化技术常常用于级联结构。第一级的输出量化噪声很大,超过了后面级的量化噪声。因此,已经有严格的级联模块的设计要求被提出,为防止噪声泄露带来的性能降低。

已经有的动态匹配技术(DEM)[5],[12],[13],例如加权数据平均算法(DWA)[14],降低了多位量化结构中对DAC的要求。这种技术把非理想的DAC带来的噪声和失真转化为噪声整形的噪声。DEM技术需要在转换器的反馈回路中加入额外的数字模块,在每个时钟周期中随机的使用单位元素。这个随机发生器带来的延迟会限制实际实施中的时钟频率。

设计的转换器采用单环多位量化△sum;拓扑,结合高精度和低采样率。在三阶四位拓扑结构的反馈环路结构中使用DWA,以减少对DACs的精度要求。结构框图如图1所示。用[6]中的方法优化环路的系数,达到最大的SNR,同时保证稳定性。

与三阶单比特的设计比较,精度提高40dB的原因有以下两个:

- 在量化器中每提高一比特的量化,量化误差的幅度就减小一半。因此4位量化器提高的精度达到了18dB。

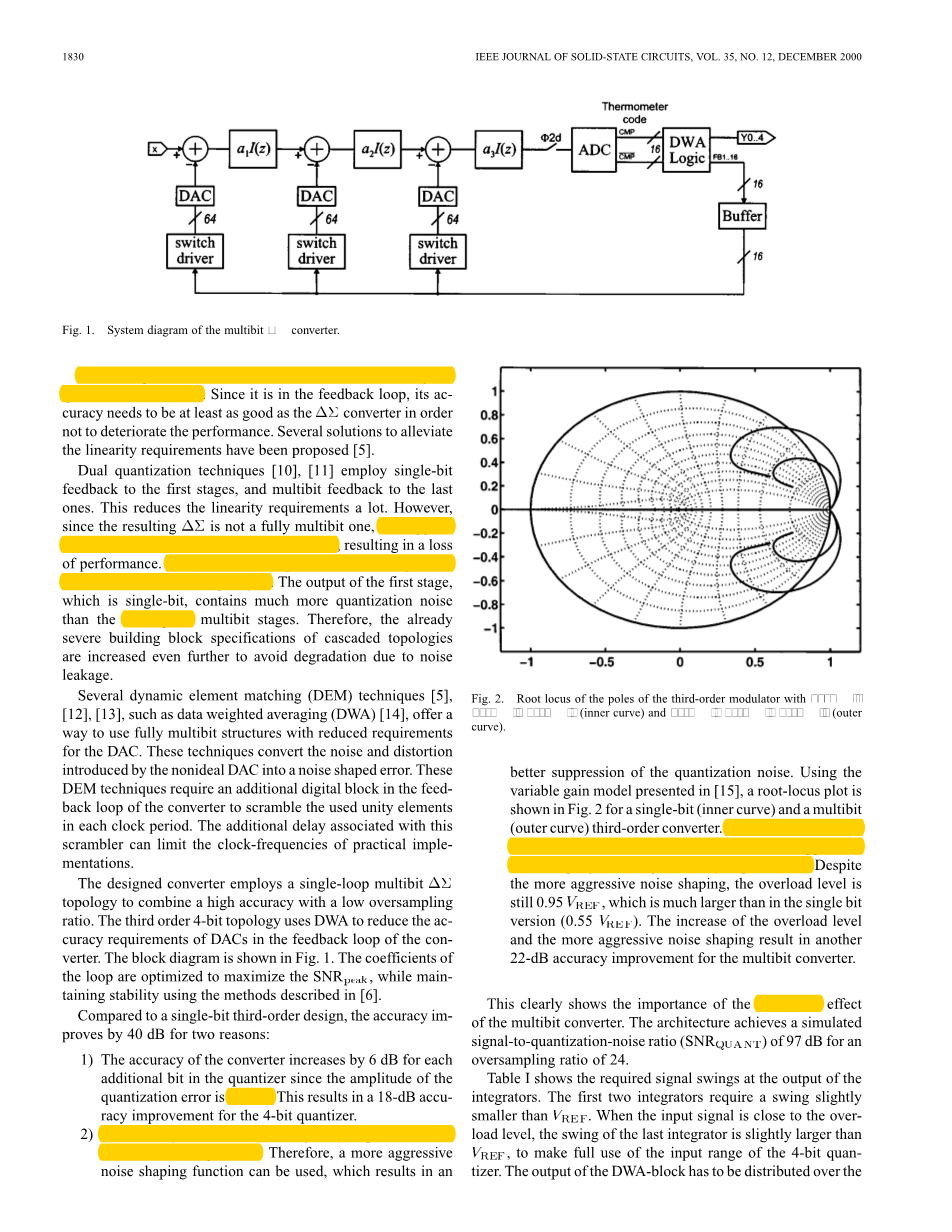

- 转换器的稳定性由于量化器的稳定性的提高而大大提高。因此,更好的噪声整形函数使用,导致对量化噪声有更好的抑制。用[15]中的可变增益模型,根轨迹于如图2所示,其中里面的曲线为单比特三阶转化器的,外面的曲线为多位三阶转化器的。多位转化器环路系数的提高导致更好的噪声整形效果,达到更高的精度。除了更好的噪声整形效果,过载电压任是0.95,比的更大。过载电压的提高和更好的噪声整形导致多位量化转化器的精度提高22dB。

上面叙述清楚的显示稳定性效应对多位转化器很重要。仿真的信号量化噪声比率()在过采样率为24的情况下为97dB。

表Ⅰ,积分器的输出需要的摆幅。前两个积分器需要的摆幅稍微比小。为了充分应用4-bit量化器的输入范围,当输入信号的幅度接近过载电压时,最后一个积分器的输出摆幅稍微比大。DWA模块的输出必须分配到整个芯片,DAC开关反馈的本地驱动。因此,内嵌缓冲解决教的大的门电容和线电容的问题。

图2 三阶调制器的根轨迹(里面的曲线:a1=0.2,a2=0.5,a3=0.5;外面的曲线:a1=0.3,a2=0.8,a3=2.3)

表Ⅰ转换器的信号摆幅和反馈跟踪信号

- 积分器和DAC

为了限制转化器的功耗,最重要的是保持电容的尺寸尽量小,因为这样减小了积分器的电容负载。因此,积分器和DAC结合,通过把采样电容分成16个平行单位电容,这样的电容可以分别连接到。这样的设计可以使反馈回路不使用额外的电容,这样可以避免额外的噪声、积分器的负载电容。因此全差分的使用使提高了3dB。除这些好处外,全差分也提供其他的好处,如减少偶次谐波,提高电源抑制比,减小时钟馈通。

如果噪声的水平对于16-bit的转化器是足够的,采样电容需要3.2pF,需要200fF的单位电容。DWA的利用(第三部分的C)使这些单位电容的匹配度对于转化器是足够的。意味着采样电容的大小任被噪声所决定,而不是被DAC的匹配度决定。所以,和传统的单比特应用比较,多位DAC不需要过多的消耗跨导放大器的能量,过多的硬件条件被限制。

积分器和DAC的实现如图3(a)所示。在时钟相,被拆分成16个单位电容的采样电容采入输入信号。在时钟相,反馈的DAC连接每个单位电容低端到。由于所有的开关通过传输门实现,对于每个单位电容需要四个控制信号。这64个信号需要从DWA模块的输出分配到每个反馈DAC。这样在缓冲中需要更多的功耗(由于线电容)和更多的线面积。为了减小反馈信号的数目和驱动功耗,如图3(b)所示的本地开关驱动器用在每个单位电容的前面。这种电路在(稍微比的翻转提前)为传输门产生控制信号,来自每个单位电容的信号。注意到,的时序对积分器的正确操作是至关重要的,零到零的重叠应该被保持,在驱动的输出和时。驱动信号可以被最小化,由于负载电容是十分小。与此同时,他们的功耗被限制。

这种DAC实现的缺点是信号的负载依赖于参考电压。对于单端实现,每一个单位电容在采样相被充电到的结尾,在单位电容上的电荷是,依赖于量化器的反馈。如果等于连接到 的电容的数目,被释放的电压缓冲上的电荷在某一时钟周期是。从抽取的电荷等于。这样显示参考电压缓冲器的负载电容是决定于信号的,由于。因此从缓冲器抽取的电荷也依赖于输入电压。信号依赖于缓冲的负载能产生严重谐波失真。

通过使用差分电路,这样的问题能减轻。从抽取的电荷等于。参考电压缓冲器的电容负载不在依赖于信号。然而,从参考电压抽取的电荷还是依赖于输入信号。

因此,为了避免谐波失真,缓冲参考电压的电路应该被特别的关注。然而,缓冲器的功耗成为sum;△转化器总功耗的重要考虑的部分。这个转化器使用外部对称电压1V。

图3 积分器和反馈DAC的具体实现

图4 开关电容积分器的全部模型(a)采样相(b)积分相

Ⅲ.行为仿真

- 积分器的非理想性

对于行为模型中的几种非理想[8]因素,可用来决定不同模块的参数设置。主要的非理想因素是运放的有限增益,有限的环路极点,开关的非零导通电阻,开关电阻的非线性。

在[8]中,开关电容积分器的增益带宽积可以表示为

(1)

(2)

这个公式中是积分器系数,是采样电容和积分电容,是运放输入和输出的寄生电容。当开关的非零电阻被计入,增益带宽积减小到

(3)以上的公式显示当对转换器的频率响应进行优化时,开关电阻和应该被同时考虑。提高导致运放消耗更多的功耗,然而更小的开关电阻R需要更大的开关尺寸,因此有更多的时钟馈通,时钟的负载电容会更大。这样的情况近似等于1。

- 转换速率

开关电容中另一个重要的非理想效应为运放的建立。如图4是积分器的详细模型和图3(a)中的DAC。图4中包括了运放输入和输出的寄生电容()。为了和文献[8]中的符号对应,在信号链路上的电阻等于R。因此,16个平行支路上的单位电容的开关值为R/32。运放的转换效应结合电流特性进行分析,如图5所示,大的节点电压,运放输出最大的输出电流。决定于来自量化器的反馈数字。分别代表连接到的单位电容的个数。的结构。它的重要性将在后面进行讨论。需要的转换速率计算如下

(4)

在公式(2)中给出。

图5 OTA转换输出电流模型

图6 积分器的全模型输出波形(a)没有电阻(b)具有电阻

细线是来自电路的仿真波形图

转换最可能发生在积分相的开始。采样电容上的采样电压接入到运放的端口,引起的大电压峰值可能驱动OTA进入转换情况。

不包含开关电阻的推导已经提出[17][18]。这些模型显示包括寄生电容是非常重要的,因为,运放的输入节点,在积分相由及时的电荷分配减小了电压。然而,两个重要的扩展需要添加到这些模型中,使之分析更精确,包括非零的开关电阻和下一级的采样操作。最后图4的模型给出非常复杂的分析表达式,由于节点数急剧的增加。因此,图4中的微分方程在MATLAB中进行数值解。

图6(a)显示了没有开关电阻的积分器的输入和输出节点的响应波形,然而,图6(b)是有开关电阻的波形。这清晰地显示这个模型和电路仿真非常的相近。横线显示转换情况的限制,由公式给出。这些波形的比较清晰的显示电阻的两个重要效应。第一,在的开始,由于不再有电容之间的电荷分布,峰值减小了。第二,由于在信号链路上有RC时间常数,峰值更加平缓。由于在节点的峰值更小,运放的转换速率将更小,运放将输出更小的电流。因此,由于电阻的原因,运放的截止频率减小到,在第三部分的A中进行了解释。这些效应导致了更慢的建立。

上面描述的波形显示,有必要对下一级的采样操作进行分析。在的开始,连接到OTA的输出,可以明显的观察到输出的电压降。注意到显示采样的降低,所以积分电容电荷没被影响。由于这个峰值,OTA在也处于转换的情况。为了确定上正确的采样电压,这个峰值也应该建立。因此,下一级的采样需要被考虑。

图7 SNR和开关电阻、OTA 图8 每一个建立时间的时钟周期的相关值

的最大输出电流的曲线

对五种不同的开关电阻和OTA的最大电流进行仿真。图7显示了△sum;转换器的SNR,图8显示第一个积分器在多个时钟周期中的转换。当开关电阻增加,需要更大的实现△sum;转换器全部性能,但是转换会更慢,由于峰值被平滑了。因为开关电阻的增加,减小,需要更多的时间进行建立。这意味着在一个周期中,用在转换的时间减小,因为需要留给OTA的线性建立更多的时间,这就需要更大的。当开关电阻变得很大,建立变得很慢,这样减小了转换器的SNR,即使非常大以使转换不再发生。

与单比特转换器比较,多位转换器在实现上更加容

全文共11399字,剩余内容已隐藏,支付完成后下载完整资料

资料编号:[144603],资料为PDF文档或Word文档,PDF文档可免费转换为Word