英语原文共 8 页,剩余内容已隐藏,支付完成后下载完整资料

误码测试的新方法及其实现

摘要

位同步和序列同步是误码测试仪中的两个关键技术。在传统误码测试仪中,数字锁相环应用于位同步和序列同步,通过序列实现同步相关,导致在低速位和序列同步。本文提出了用新的方法实现位序同步,这是代码边缘捕获方法和注入接收序列方法。FPGA被用来实现测试仪的所有功能模块。调试和仿真结果显示实现比特同步的时间小于代码周期的3 /8。只有一种m序列循环实现序列同步。这新的CER测试仪有许多优点,如消除伪序列同步,比位同步和序列同步时间更短,且有良好的硬件协同。

关键词:误码仪;m序列;本原多项式;位同步;伪HDB3码序列同步;

1.介绍

对于数字通信的明显特点来说,它已成为现代化信息传输的重要手段。因为在数字通信中频道衰落,符号间串扰和设备错误,他们都会导致接收器中的代码错误[ 1 ]。误码测试仪通常是用来测量通信系统的CER(CER代表码元错误率)。传统误码测试仪在数字锁相环中实现位同步[ 2,3 ],这是比较和调整阶段接收到的代码和本地生成的代码得到位同步脉冲。它需要几个码元周期达到位同步,所以它是一个低速率的[ 4 ]。序列的相关性用于实现序列同步[ 5,6 ]。有几种方法来实现它,例如,sliderelevance捕捉方法,序列relevancecatch方法和SAW组件捕捉方法。这些方法也有几个缺点,例如,有一个复杂的硬件结构和需要很长时间来实现它。微控制器常常被用作控制模块,FPGA用作逻辑模块[ 8,9 ]。因为这个这两种设备在速度上的差异,导致它们协同效果不好。本文介绍了一种新的误码测试仪。位同步和序列同步采用快速同步方法。CPU模块,发送模块,接收模块及时钟模块的系统都是基于FPGA的。FPGA芯片EP2C8Q208C8N 是Altera公司的产品[ 10 ]。

2.误码测试仪的结构和原理

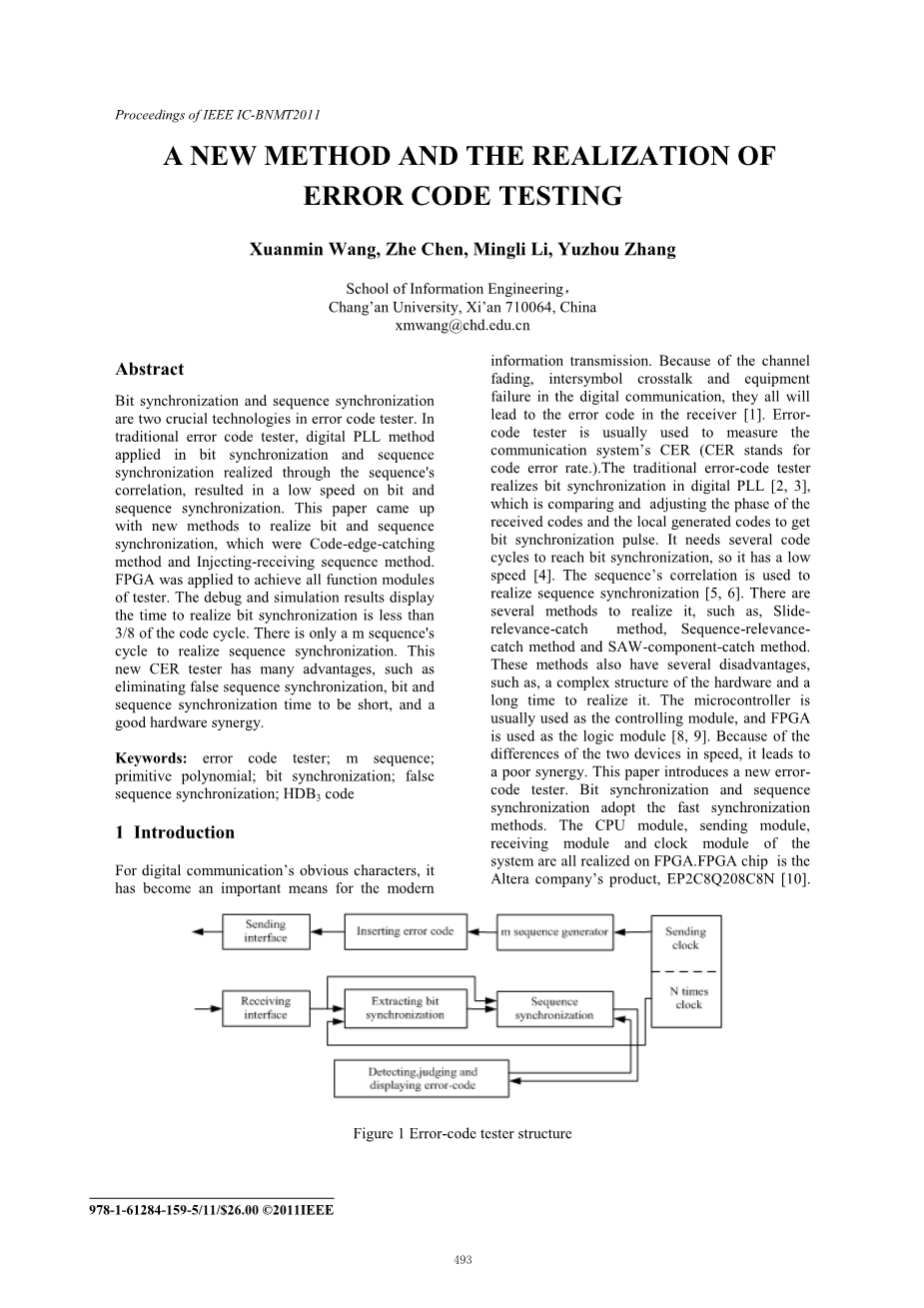

误码测试仪包括三部分,其中包括发送部分、接收部分和时钟部分,如图1所示。发送部分包括m序列发生器,插入错误代码模块和发送接口。m序列生成器用于生成伪随机序列[ 1 ]。

插入错误代码模块可以实现手工插入错误代码,用于检测通信系统的纠错码容量。发送接口是用来把NRZ转变成HDB3码,适用于频道转换。接收部分主要由接收接口,位同步提取,序列同步和检测判断错误码组成。这个接收接口主要是用来把HDB3码转变成NRZ。提取位同步模块用于从中提取位同步脉冲接收序列。这个脉冲用作本地序列发生器的时钟。序列同步模块的功能是使局部序列和接收序列同步。检测、判断和显示错误码元模块的功能是首要的,相较于从局部序列同步序列逐位获取错误码脉冲;其次,在一定时间内计算误码脉冲,然后判断计数值是否小于门槛。如果它更小,计算并显示CER。如果不是,则错误序列同步发生而且和执行序列同步了。

3 .m序列发生器结构

误码测试仪的发送端口主要功能是生成数字序列用于测试。因为m序列和伪随机序列噪声特征相似,它是用来测试通信系统错误码元。m序列发生器由线性反馈移位寄存器组成。如图2显示。图2 m是序列发生器的原理。在图2中,ak-i代表每一个国家登记。CI是每个寄存器的反馈系数。当它等于1时,寄存器被使用,反之则没有被使用。反馈功能是(1)CI值决定寄存器的反馈状态和序列的组成、周期。图2中的特征多项式是(2)。如果图2变成m序列发生器,则特征多项式必须是本原多项式。基于ITU-T,M序列周期用于数字传输的系统测量值为32767,即。本原多项式是(3)。在此基础上,我们可以很容易生成出m序列。为了防止m序列发生器在不确定条件下生成全零状态,导致一个无休止的循环,我们把所有D触发器的Q输出连接到与非门的输入,并连接与非门的输出到第一D触发器的设置端口。通过这个方式,发生器就可以自己启动。

4.插入误码模块

发送端口的另一个重要功能是插入误码。首先,我们插入误码发送序列,然后检测误码在编码传输系统接收端进行纠错的能力。按下误码插入键。插入错误代码原理图如图3所示。NRZ0是不插入序列的误码。 NRZ1是序列,即插入误码。 KEY是输出信号插入键。 CLKT是发送时钟。按键一次,KEY端口将产生一个高电平脉冲。它的上升沿可以到达输出端口,当D1等于1时,插入跟踪逻辑。随着CLKT的第一个时钟来临,第一个寄存器的输出端口D2等于1,使数据选择器选择A端口,然后发送的序列NRZ0将被反转。同时,它也插入跟踪逻辑,当D1等于0时,即CLKT的第二个脉冲,第二个寄存器会产生误码,首先输出端口等于0,这使得数据选择器选择B端口。那么NRZ0将不会插入误码输出。所以按键一次,你只能插入一个错误代码。图4显示了插入错误代码的模拟结果。从结果中可以找到按键,一次只生成一个错误代码,无论你按键多久。

5.提取位同步模块

提取位同步模块的功能是将从接收到的位同步信号序列,用作本地时钟序列发生器。提取位同步模块包括边缘捕捉逻辑,寄存器和计数器,可以设置如图5所示。NRZ2是改变的NRZ序列从HDB3序列通过接口接收。CLKR是位同步信号提取位同步模块。CLK0是由时钟模块提供,其频率是NRZ2的7倍。提取位同步模块的工作原理如下。随着收到的NRZ2的正脉冲来临,边缘捕捉逻辑的输出E1,等于1。第一个CLK0的脉冲来了之后,输出了寄存器的E2,等于1.这使计数器处于设置状态,即计数器的输入#39;0000#39;,边缘捕捉逻辑E1的输出是0。第二个CLK0的脉冲来时,E2的输出为0,计数器计数对于CLK0的脉冲为八进制。循环计数器输出CLKR等于NRZ2正脉冲的代码宽度。CLKR周期跟踪NRZ2的上升沿正脉冲。跟踪滞后的时间脉冲是代码宽度的3/8。图5提供位同步模块。在NRZ2端口的正脉冲后,计数器仍然以八进制计数。所以当有几个连续的一和零,计数器可以在一定时间内保证CLKR的输出端口可以导出位同步脉冲,符合要求。当有新的来自NRZ2端口的正脉冲的时候,提取位同步模块可以像之前一样产生一个新的位同步序列。

6.序列同步模块

序列同步的功能模块是使接收到的序列和本地序列同步。所以我们可以比较两个序列并提取错误代码。因为发送序列是一个m序列,本地序列发生器应该与结束部分具有相同的结构。而m序列是一个周期性的序列,所以比较接收序列和本地序列,应该在一个周期内从相同的位置开始。在比较之前,接收序列和本地序列必须同步。将接收序列方法应用于序列同步。从接收中提取同步脉冲部分用作本地序列的时钟生成。来自接收序列的15个连续码元被加入到本地序列发生器作为起始状态。所以它是从起始状态生成本地序列。由于本地序列发生器和发送端口具有相同的结构,如果加入15个码元正确,代码生成在发送后是一样的,他们是同步的。图6显示了序列同步模块。本地序列发生器是由寄存器,F1-F15和XOR2门组成的。它的时钟CLKR,来自位同步模块。

错误端口的输出是错误代码脉冲,这是两个序列比较的结果。这种按顺序添加序列是关键。当你按下它时,S端口的输出数据选择器是一个高层次的脉冲,并且NRZ2是出口。后面的15个周期时钟,所接收的序列在编码一个周期被注入到本地序列产生器。在此期间,逻辑为0错误端口输出为0。在此之后,数据选择器选择XOR2作为输出。这个本地序列发生器生成基于注入的15码元信号的。局部序列由XOR2门和收到的出口D触发完成序列同步。xor1是用于比较同一位置的两序列码。如果他们都不一样,错误端口会导出错误编码脉冲。当你注入序列按下键,注入的高级时间端口不严格等于15个周期的时钟和大于或等于15个周期的时钟。因此,它很容易实现。

图7显示了该位的仿真结果和序列同步。 从模拟结果中,我们知道位同步脉冲,时钟,跟踪接收到正脉冲的上升沿,NRZ2。按一下添加键,就可以实现序列同步一次。 插入时发送端口的错误代码,可以检测ERROR端口中有一个错误代码脉冲。图7位同步和序列同步检测CER的仿真结果

7.误码统计和CER计算

如果大于阈值,15个连续注入码可能包含错误码。在这种情况下,本地序列和发送序列可能会有所不同,顺序同步称为虚假同步。在这种情况下,CER的计算没有意义。为了防止错误同步产生,当错误代码计数器的值大于阈值,我们应该重新计算。如果做到这一点,连续时间结果都大于阈值。加入的序列一定包括错误代码,序列同步确定是假同步。在这个时候,我们应该注入一个新的接收序列,并做顺序同步。图8显示误码统计的过程和CER的计算。

8.结论

与传统的误码测试仪相比,这个误码测试仪具有许多特点,如,控制模块,数据处理模块和逻辑模块的发送端口和接收端口的实现是基于FPGA。这提高了协同效果和速度。该系统采用了代码边缘捕获方法实现位同步。因此,位同步时间小于一个码元周期;采用添加接收顺序法实现序列同步。只有达到它需要的一个序列周期。为了避免虚假序列同步,当连续误码计数器的值都大于阈值时,接收到的序列和本地应该再次通过按下添加键实现同步。

速率为10 MB / s到 11.3 Gb / s之间的便携式

低误码率测试仪的设计与开发

1.介绍

随着宽带光接入网络的快速发展,特别是无源光网络和FTTx技术,光纤链路监控,网络服务性能和实时质量已经成为一种重要的挑战。特别是位于复杂环境下的接入网络具有复杂的网络结构,多速率级别和各种类型的线路,增加了运营维护的成本。开发便携式BERT,具有速度范围广,体积小,重量轻,成本低,操作方便的优点,可以测量光纤链路或接入网的可靠性。目前,商业上主要存在两种类型的误码测试仪。一个是没有光端口的低速仪器,它以2.048Mb / s或155Mb / s的单个数据速率运行[4]。另一种类型的误码测试仪类似于Agilent N4903B误码测试仪和Anritsu MP1800A信号质量分析仪等。虽然它们具有光接口并且支持更广泛的和更高的速率,但是它们的应用在其高成本,大容量的现场维护和建设和重量等,受到限制。因此,本文开发了具有宽数据速率范围,低成本,小尺寸,低功耗的便携式误码测试仪,其具有电和光端口,并且支持任何速率10 Mb / s和11.3 Gb / s。此外,该误码测试仪的主要组件也可以放置在诸如光线路终端(OLT),光交叉连接(OXC)和光分插复用器(OADM)的许多光学设备中,以实现实时监测其BER性能。

2.误码测试系统的结构和原理

我们提出的误码测试系统的主要结构如图1所示。它主要由伪随机二进制序列(PRBS)发生器,误差检测器(ED),微控制器单元(MCU)和SFP(小型可插拔)光收发器组成。 MCU控制PRBS发生器和ED生成不同的模式,如,和,并使用I2C总线读取错误计数。发生器可以以10 Mb / s和11.3 Gb / s之间的任何速率输出PRBS,以适应不同速率的标准测试系统。输出信号数据速率表示为

(1)

其中CLKIN是输入参考时钟的频率。 RefRatio是参考频率比的数据,FrefRange表示参考频率范围,它们由MCU控制。 RefRatio的值可以为0,1。FrefRange由输入参考时钟决定,FrefRange值与输入参考时钟的频率范围之间的关系如表1所示。例如,如果输入参考时钟的频率为176.8 MHz,则RefRatio FrefRange可以设置为10和3。在这种情况下,可以产生具有11.3Gb / s速率的PRBS信号.PRBS可以通过差分子级别A(SMA)端口或光信号通过SFP模块输出电信号,实现电光转换。 ED模块还支持电和光输入信号。所有这些端口都严格要求传输线路,以确保输出PRBS信号和输入检测信号的信号质量。输入信号首先进入先进先出(FIFO)缓冲器,检测器将通过将输入序列与比较器中的PRBS发生器进行对比来对误差进行计数。数据通过I2C总线传输到MCU,并显示在用户操作界面。我们通过软件编程设计的方便操作的BERT接口如图2所示。软件程序主要包括串行通信部分,PRBS发生器和ED控制部分,显示部分,用于控制MCU。

3.测试系统及结果讨论

所提出的连接BERT的测试系统如图3所示。为了验证PRBS发生器和ED模块的性能,使用Anritsu MP1800A和Agilent 86100D。首先,测试设置数据速率为10 Gb / s和模式的PRBS发生器模块的性能。图4显示了PRBS发生器输出数据的眼图。单输出信号VS-p-p的振幅为227 mV,峰峰值抖动Jp-p为25.45 ps,RMS抖动JRMS为4 ps(MP1800A输出信号Jp-p为15.54 ps,JRMS为2.2 ps),考虑到其小尺寸和低损耗,这证明输出信号具有良好的抖动性能。 PRBS发生器输出数据的眼图为10 Gb / s。为了测试其精度,该信号被输入到MP1800A,因此没有检测到错误位。其次,通过使用MP1800A的错误添加设置来测试ED关于错误计数功能的准确性。来自MP1800A的输出数据分为两个信号,一个输入到MP1800A本身,另一个由我们的ED模块检测。图5是MP1800A(左)和ED模块(右)之间的比较结果。数据速率为10 Gb / s测试模式是的NRZ信号。 MP1800A显示界面和ED部分的软件窗口之间的错误次数相同,说明设计的ED模块可以与MP1800A一致地检测出错误编号。

全文共5910字,剩余内容已隐藏,支付完成后下载完整资料

资料编号:[144576],资料为PDF文档或Word文档,PDF文档可免费转换为Word

以上是毕业论文外文翻译,课题毕业论文、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。