英语原文共 12 页,剩余内容已隐藏,支付完成后下载完整资料

一个可扩展的

快速和多通道任意波形发生器

M. T. Baig, M. Johanning, A. Wiese, S. Heidbrink, M. Ziolkowski, and C. Wunderlicha

Department of Physics, University of Siegen, Walter-Flex-Strasse 3, Siegen NRW 57072, Germany

本文对多通道任意波形发生器的发展进行讲述,这个波形发生器能同时产生24个独立通道的任意电压波形,且动态更新速率高达25 Mbps。实时执行的单个波形或一多个相继的波形序列,通过用户可编程任意序列顺序的控制下提供的一个独立的定序器电路的使用现场可编程门阵列来实现。该装置是使用内部时钟操作,可以通过晶体管 - 晶体管的装置同步到其它设备逻辑(TTL)脉冲。该装置可以在的范围内提供多达24个独立的幅值高达plusmn;9伏的电压,而动态更新速率高达25 Mbps,功率消耗小于35W。每个通道可以为16个运行时最小开关延迟为160 ns的独立的任意波形编程。该装置具有250mu;VRMS低噪声,并提供与长期操作时间漂移率低于10mu;V/分,最大偏差小于一个稳定的时间plusmn;300mu;V的波形 。

- 目的

离子阱在量子信息科学领域很有发展潜力;1-4,尤其是微结构保罗陷阱非常适合用于此目的。它们可以有为原子的诱捕,处理,以及存储提供多个区域。为量子信息处理缩放这些陷阱需要大量的独立的高带宽,低噪声电压信号。

在这种方法中,量子位(量子比特)的寄存器存储在激光冷却俘获离子的内部状态(形成一个维格纳晶体),而在动生一些实施正常模式下的状态。越来越多的维格纳晶体长度变得难以冷却,以防止环境影响,因而受到消相干。依赖于

量子叠加和缠绕的计算力量的操作方式是有害的。拆分量子寄存器到管理规模的结晶并在一个量子网络的需求上使他们交络被认为是一个有前途的和直接的解决方案。这可以在分段的离子阱实现,而离子阱里贮存,穿梭和加工的区域是由大量的DC电极来实现的。这些类型的陷阱通常被视为一个前提条件使用可伸缩的量子信息处理囚禁离子。

这样一个分区量子的具体实现寄存器需要以离子穿梭才能够交换独立的结晶,这是之间的信息与情绪状态的低发热最好做。这可以通过在绝热方式中的离子穿梭来实现,但要以长穿梭时间为代价,或者通过为低热进行优化的非绝热方式来实现。后者需要快速更新电压。

这种类型的量子信息处理的另一个组成部分是拆分和合并离子的字符串,并需要精确控制大量电压。处理量子信息的各种建议的存在在其他的网络模型,或依靠可能在离子阱中生成的高度纠缠图态的测量基础量子计算。穿梭和相互作用的剪裁不仅可以通过操纵直流电压完成的,但也将RF电压用于离子串的径向捕获。通用量子处理器将是一个现场可编程陷阵(FPTA)。独立的任意时间依赖性电位(例如,DC和RF电压的总和)可以被施加到FPTA的每个元件,允许创建任意诱捕电位(相对于一个固定的优化的设计20点阵)和不同类型的点阵的调查以及量子模拟物与单个可编程陷阱(一个类似的概念是在参考文献中讨论。)对某些类型离子捕集尺寸,这里介绍的设备已经实现所有必要的要求。这种类型的应用可能需要 - 根据所选择的离子和阱设计- 更高的振幅或更新速率比所提供的这里所描述的设备;以及,为了减少加热和该RF成分的滤波的窄带。同样,量子模拟器需要高度的控制,以模拟其他量子的特征系统。截留的离子间的相互作用能进行定制以模仿一个完全不同的量子系统,例如,通过塑造轴向捕获潜能。

此应用中,也需要大量的独立电压。

此外,在实验量子光学领域,激光场通常被用来操纵内部或原子的运动状态,并需要在时间和空间上形成。成形激光脉冲的时间轮廓,可以实现利用声光调制器(AOM),其中控制信号可用于产生任意的幅度和激光的频率模式。激光的空间分布光束能够通过一个空间光调制器(SLM)被操纵,通常被实现为液晶显示器(LCD)或数字微镜器件。该SLMs往往需要数字信号用于使用脉冲宽度调制控制,但模拟实施方案可能存在需要再次大集独立的电压。以相同的方式,光谱和大带宽激光器相应的时间特性和频谱可以操纵.其他应用量子光学社区,例如,该控制信号代来塑造中性磁或偶极陷阱原子29,30和运用短信,进行波前感应,而自适应成像和全息还需要大量的个别电压。市售设备不符合电压的精确要求,即快速更新速度与需要量子光学实验速度相结合。 本文在设计开发,和一个特征报告可扩展性,快速,多通道任意波形发生器(AWG),以满足先进的量子要求光学实验。

- 硬件架构

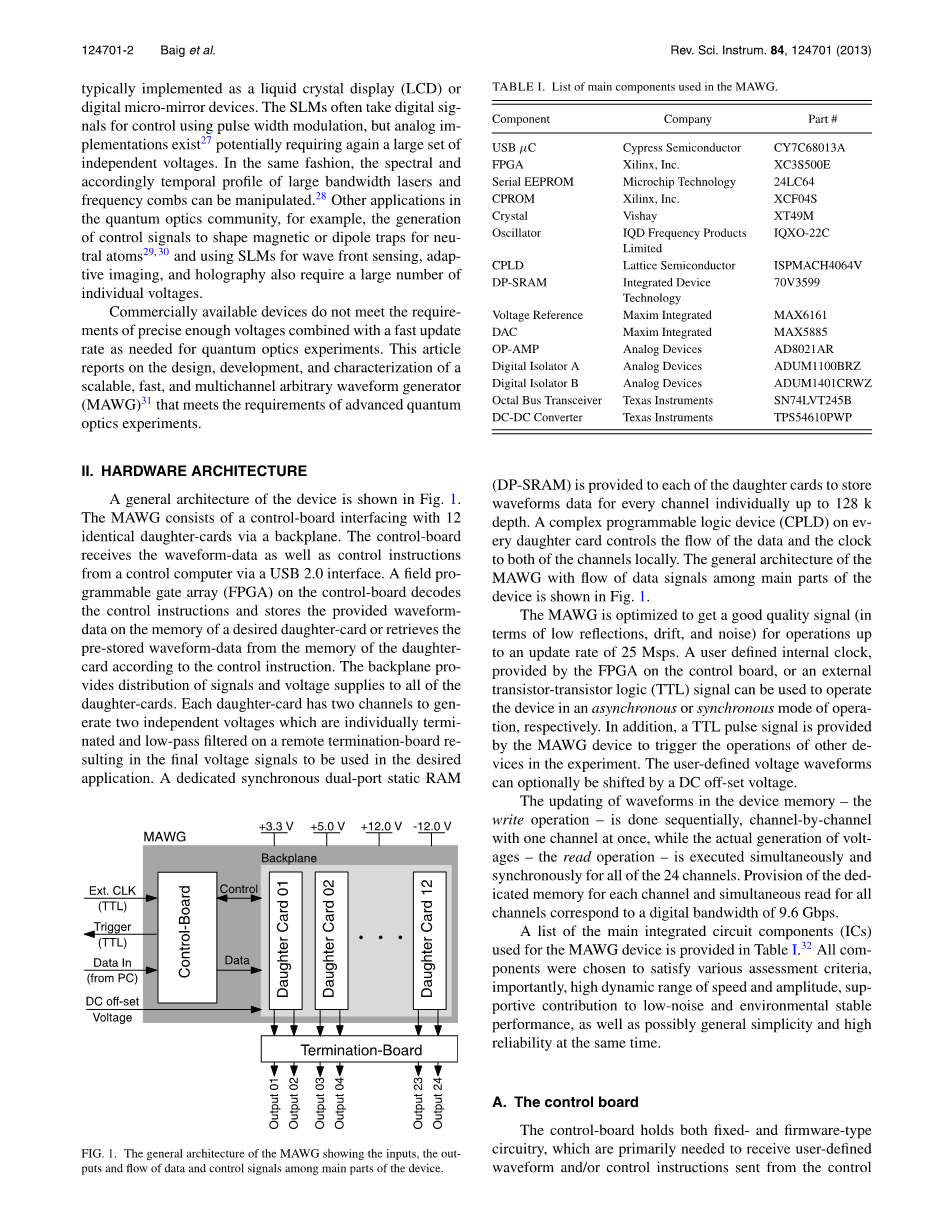

该装置的一般结构示于图1所示。该MAWG通过背板由一个含12个相同的子卡接口的控制电路板组成,该控制板接收波形数据以及从通过USB2.0接口控制计算机。根据该控制指令,控制板上现场可编程门阵列(FPGA)解码控制指令和存储所提供的波形数据上的期望子卡的存储器或获取从子卡的存储器预先存储波形数据背板提供信号和电压用品配送到所有的子卡。每个子卡有两个通道来产生这是单独终止两个独立的电压和低通滤波上得到的远程终端板在最终的电压信号中的需要,可使用应用。为了每个通道单独多达128K的深度,专用同步双端口静态RAM(DP-SRAM)被提供给为每个子卡存储波形数据。一个复杂可编程逻辑器件(CPLD)上每子卡控制数据和时钟的流动以本地的渠道。MAWG的一般结构用的主要部分之间的数据信号的流装置被示于图1所示。

图1 MAWG的输入,输出和装置主要部分之间的数据流动和控制信号

该MAWG被优化以获得良好的质量信号(在较低的反射,漂移和噪声)运营起来的更新速率至25 Msps。定义的内部时钟的用户,通过在控制板上的FPGA,或外部提供的晶体管 - 晶体管逻辑(TTL)信号可分别用于操作该设备在操作中的异步或同步模式中。此外,由MAWG设备给其他在实验中装置的操作提供了一种TTL脉冲信号触发。用户定义的电压波形可任选地通过一个直流截止组电压偏移。在装置记忆-写入操作-中的波形更新率与一个通道的更新是同步执行的,而实际生成的电压-读操作-对所有24个信道同步执行。每个通道同时读取所有通道的专用内存,提供对应于9.6 Gbps的数字带宽。

主集成电路组件的列表(集成电路)用于MAWG设备表I.被提供选择的所有组件,以满足不同的考核标准,重要的是,速度和幅度的高动态范围,支持低噪音和环保贡献稳定性能,以及可能一般简单性和高同时可靠性。

表1 在MAWG元器件清单

|

元件 公司 型号 |

||

|

USB mu;C |

赛普拉斯半导体公司 |

CY7C68013A |

|

FPGA |

Xilinx公司 |

XC3S500E |

|

串行EEPROM |

微芯片科技 |

24LC64 |

|

CPROM |

Xilinx公司 |

XCF04S |

|

晶振 |

Vishay公司 |

XT49M |

|

振荡器 |

伊拉克第纳尔频率产品 有限公司 |

IQXO-22C |

|

CPLD |

莱迪思半导体公司 |

ISPMACH4064V |

|

DP-SRAM |

集成设备 技术公司 |

70V3599 |

|

参考电压 |

美信集成公司 |

MAX6161 |

|

DAC |

美信集成公司 |

MAX5885 |

|

OP-AMP |

模拟设备公司 |

AD8021AR |

|

数字隔离器A |

模拟设备公司 |

ADUM1100BRZ |

|

数字隔离器B |

模拟设备公司 |

ADUM1401CRWZ |

|

八路总线收发器 |

德州仪器公司 |

SN74LVT245B |

|

DC─DC变换器 |

德州仪器公司 |

TPS54610PWP |

- 控制板

控制板上同时拥有固定和固件型电路,其主要是需要接收用户定义波形和/或从控制计算机发送控制指令,进而处理并把它们传送到通过以受控的方式在底板上的子卡。

从控制计算机通过USB微控制器(mu;C)所接收,再经由USB接口把数据发送到一个2字节字格式FPGA中。该FPGA分析数据,并提供一个面向单字节输出,在指令或波形数据的情况下直接或者通过其内部的块RAM到背板上。在控制板上的所有输出随后由八进制总线所提供的信号电流的增强收发器隔离。充电后,可编程只读存储器(EPROM)和串行电可擦除可编程只读存储器(EEPROM)被用来自动配置FPGA和USB mu;C。详细说明该控制板组件和数据流如图2所示。

图2.控制板上的组件之间的数据和信号流。USBmu;C经USB接收来自控制计算机的数据,并通过数字隔离器和八进制总线收发器传送该数据到背板FPGA中。可选TTL输入和一个TTL输出是还通过数字隔离器提供。CPROM和EEPROM被提供到分别自动配置在FPGA和USBmu;C。

控制板上的元件所需要的电压(1.2 V,2.5 V,3.3 V和5.0 V)由单相DC-DC变换而得的 5.0 V电源供给,电隔离的TTL兼容输入和输出被提供到同步装置的操作在实验中的装置的其余部分。 TTL输入可以被用来作为内部时钟触发器或施加信号作为同步使用的外部时钟MAWG。

一个24 MHz晶振被USBmu;C使用去产生内部USB数据传输所需要的480 MHz和48 MHz的时钟。此外,由FPGA使用的一个50MHz的板载振荡器是通过内部装置产生的时钟信号而分频,这是MAWG写入和该的读取操作所需的。

B 带子卡的背卡

背板拥有12个相同的子卡,每个子卡共享一个共同的数据总线,控制总线和地址总线。从控制基板接收的波形数据通过背板输送到一个子卡上的信道进行写操作。所有公共线路在背板上进行阻抗匹配和电阻端接。 3个电源电压 3.3V和plusmn;12V(可选plusmn;15V)通过专用的外接电源产生并分配给每个子卡背板。

所有电源线由在背板入口处的齐纳二极管保护。

子卡包含电路产生两个独立的电压。子卡上所使用的关键部件数据流和控制信号如图3所示。CPLD控制信号由子卡接收并为数模转换器产生时钟脉冲,而(DAC)DP-SRAM随控制信号显示在相同的子卡上。当MAWG得写操作指令被执行或者从DP的SRAM的一个特定的地址送到执行MAWG的读操作所需的DAC进行传递活动时 ,控制信号就管理存储数据到DP-SRAM时的一个特定地址。该CPLD和DP-SRAM满足各自的子卡的通道。每16位DAC转换各自的数字代码为一对模拟信号并把它提供到运算放大器(OP-AMP)。由 子卡提供的输出电压被耦合到110Ώ阻性的屏蔽双绞线电缆上。该子卡的关键成分列于表Ⅰ中列出。

图3.子卡电路框图,数字数据和控制信号控制信号从FPGA的控制板流到CPLD,在子卡上的DP-SRAM随后的框图是通道、终端电阻及低通滤波器的框图。

该子卡上的通道可以在两种操作操作模式下:停止时钟模式和继续时钟模式。 在停止时钟模式下的通道DAC持有最后电压序列的值,电压序列从DP-SRAM被读取,而不是从持续时钟模式的DAC得到一个连续的时钟的CPLD得到进一步的时钟信号,并以户定义的时钟更新速率刷新存储器中电压序列的最后一个值读。

C.子卡上的通道

子卡上的单通道由一个互补电流型输出的16位DAC,低噪声高速的差分配置增益等于10的运算放大器。DAC将写操作预先存储在DP-SRAM中的用户定义的

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[146516],资料为PDF文档或Word文档,PDF文档可免费转换为Word