英语原文共 40 页,剩余内容已隐藏,支付完成后下载完整资料

LPC2114 / 2124

单芯片16 / 32位微控制器;

128 / 256 KB ISP/IAP 10位ADC闪存

一般描述

LPC2114 / 2124是基于实时仿真16位和32位ARM7TDMI-S CPU和嵌入式跟踪支持,连同128 / 256 KB的嵌入式高速闪存的记忆。128位宽度的内存接口和一个独特的加速器架构使32位代码执行在最高时钟速率。对于关键代码大小的应用程序,替代的16位Thumb模式将代码减少了超过30%最小性能惩罚。

其紧凑的64引脚封装,低功耗,各32位定时器,4通道10位ADC,PWM通道和46个快速GPIO线路和九个外部中断引脚,这些微控制器特别适用于工业控制、医疗系统、访问控制和销售点。具有宽范围的串行通信接口,它们也非常适合于通信阳离子网关、协议转换器和嵌入式软调制解调器以及许多其他通用应用程序。

备注:在整个数据表,术语LPC2114 / 2124将适用于设备有无/ 00或01后缀。00 /或/ 01后缀将使用来自其他设备的唯一的区别很有必要。

特征

2.1 主要特点通过LPC2114 / 2124 / 01设备带来

- 快速GPIO端口启用端口引脚切换了3.5倍,比原装置更快。他们也允许一个端口引脚在任何时间内读取,无论其功能。

- ADC专用结果寄存器减少中断开销。当配置为数字I/O功能时ADC板为5V容限。

- UART0 / 1包括小数波特率发生器,自动波特率能力和完全硬件实现手动流量控制

- 缓冲SSP串行控制器支持SPI,4线SSI和微格式。

- SPI可编程数据长度和主模式增强。

- 多样的代码读保护(CRP)使不同的安全级别是实施。这一特征在LPC2114 / 2124 / 00设备也有。

- 通用定时器可以作为外部事件计数器。

2.2 所有设备通用的关键特性

(1)16位和32位ARM7TDMI-S微控制器在小LQFP64封装。

(2)16 KB片上静态RAM

(3)128 / 256 KB的片上闪存程序存储器。128位宽接口/加速器使高速60MHz操作。

- 在系统编程(ISP)和应用程序编程(IAP)通过片上引导软件。闪存程序需要1毫秒每512 B行。单扇区或全芯片擦除需要400毫秒。

- 嵌入式ICE-RT接口使断点和观察点。中断服务程序可以继续执行任务,而前景是对片内RealMonitor软件调试。

- 嵌入式Trace Macrocell(ETM)使非侵入式高速实时跟踪指令执行。

- 转换时间为2.44micro;S.四通道10位ADC。

- 两个32位定时器(四个捕获和四个比较通道),PWM单元(六输出),实时时钟(RTC)和看门狗。

- 多个串行接口包括两个UART(16C550),快速I2C总线(400 kbit/s)和两个SPI。

- 60 MHz的最大CPU时钟可从可编程的100micro;S.沉降时间片内锁相环

- 向量中断控制器可配置优先级和向量地址。

- 高达四十六个5V容限的通用I / O引脚。高达九个边缘或水平敏感外部中断引脚可用。

- 片上晶体振荡器的工作范围为1MHz至30MHz。

- 两个低功耗模式,空闲和断电。

- 处理器唤醒从断电模式通过外部中断

- 个人启用/禁用电源优化外围功能。

- 双电源:

CPU工作电压范围为1.65 V至1.95 V(1.8 V值为0.15 V)。

输入/输出电源电压范围为3 V至3.6 V(3.3 V值为10%)与5 V容

限I / O 焊盘。16位和32位ARM7TDMI-S处理器。

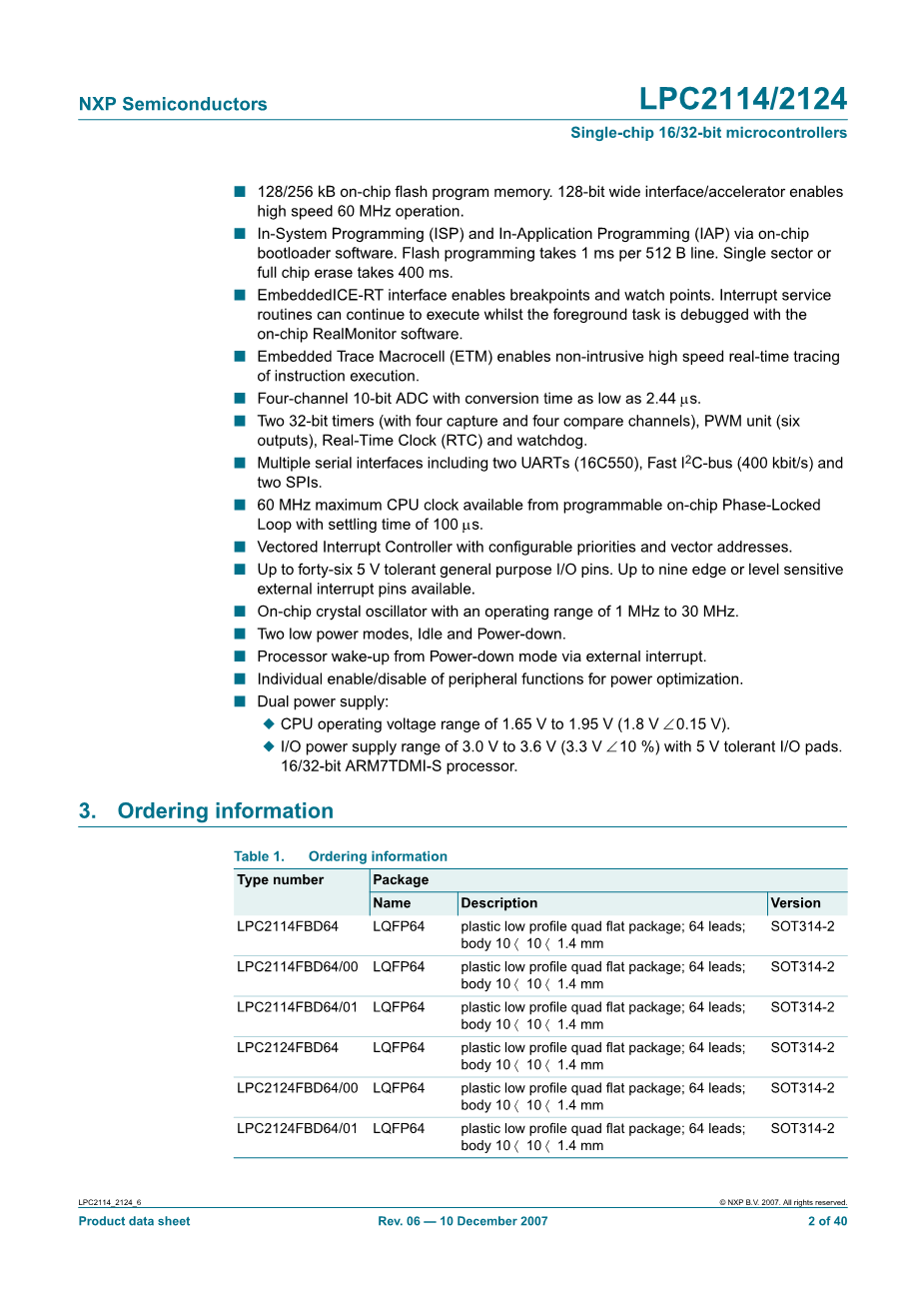

3.订购须知

表格 1 订购须知

3.1 订购选项

表格 2 订购选项

4.框图

图 1 框图

(1)与GPIO共享

(2)当测试/调试接口使用GPIO /其他功能共享这些引脚不可用。

(3)SSP接口和高速GPIO只可在LPC2114 / 01和LPC2124 / 01中获得。

5.引脚信息

5.1 引脚

图 2 引脚配置

引脚配置和设备不带/ 00 / 01后缀是相同的。

5.2 引脚描述

表格 3 引脚描述

功能描述

LPC2114 / 2124系统和外围功能的细节在下面的章节中描述。

6.1 体系结构

ARM7TDMI是一种通用的32位微处理器,它提供了高性能和低功耗。ARM体系结构是基于精简指令集计算机(RISC)的,并且指令集和相关的译码机制比那些微程序控制的复杂指令集计算机简单得多。这种简化实现了高的指令吞吐量和出色的实时中断响应,所以说这是一种体积小、性价比高的处理器核。

采用流水线技术使处理和存储系统可以连续操作。通常情况下,当一个指令正在执行,下一条指令被译码,第三条指令从存储器中取出。

ARM7TDMI-S处理器也采用了独特的体系结构策略Thumb,使其能够完美地适应有存储限制的高容量的应用和有代码密度问题的应用。

Thumb的关键是超简指令集。从本质上讲,ARM7TDMI-S处理器有两个指令集:

标准32位ARM指令集。

16位Thumb指令集。

Thumb集的16位指令长度使它具有了标准ARM代码的2倍的密度,同时,相对于使用16位寄存器的传统15位处理器,它保留了更多的ARM性能,这是因为Thumb代码操作与ARM代码一样,都是在32位寄存器中。

Thumb代码是能够达到ARM的代码规模的65%,但其性能相当于连接到一个16位存储器系统的ARM处理器性能的160%。

6.2片上闪存程序存储器

LPC2114 / 2124分别包含一个128 KB和256 KB的闪存记忆系统。此存储器可用于代码和数据存储。该闪存存储器编程可以实现几个方法。它可以通过串行口在系统中编程。当应用程序运行时也可以擦除与/或程序的闪存,允许很大程度的数据存储领域的固件升级的灵活性,当片上引导程序运行时,120 KB和248 KB的闪存可用内存的用户代码。。

LPC2114 / 2124闪存记忆提供了至少100000次擦除/写周期和20年的数据保留。

在片上引导程序(如修订1.60)提供代码读保护(CRP)的片上存储器闪存LPC2114 / 2124,当启用CRP时,JTAG调试端口和ISP命令访问任意一个片上RAM或闪存的记忆被禁用,然而,ISP闪存擦除命令可以在任何时间执行(无论CRP是开或关),除了CRP是由完整的片上用户闪存删除了,或者CRP关闭,充分访问通过JTAG与/或ISP的芯片恢复。

6.3片上静态RAM

片上静态RAM可用于代码和/或数据存储,该SRAM可访问为8位,16位,和32位,LPC2114 / 2124提供静态RAM KB 16。

6.4内存映射

LPC2114 / 2124内存映射包含几个不同的区域,如图所示图3。

此外,CPU的中断向量可以重新映射到允许他们存储在闪存内存(默认)或片内静态RAM。这是在第6.17节中描述的“系统控制”。

图 3 存储映射

6.5中断控制器

向量中断控制器(VIC)接受所有的中断请求输入并将其分类为快速中断请求(FIQ),中断请求(IRQ),和非向量IRQ为定义的可编程设置。可编程分配方案意味着优先级的中断从各种外设可以动态分配和调整。

快速中断请求(FIQ)具有最高的优先级。如果多个请求分配给FIQ,VIC将产生FIQ信号到ARM处理器的请求。当只有一个要求被分给FIQ时,将会将可能快的事项FIQ延迟,因为这时FIQ服务程序可以简单地开始处理设备。但如果多个请求分配给FIQ ,FIQ服务程序可以读取VIC,标识FIQ中断源请求中断。

向量IRQ具有中等优先级。16个中断请求可以被分配到这个类别,任何的中断请求可以被分配给任何16个向量槽,在WHICH插槽0具有最高优先级,插槽15最低。

非向量IRQ的优先级最低。

VIC将从所有的向量和非向量IRQ产生IRQ信号对ARM处理器的要求。中断服务程序可以从VIC读取寄存器并跳转到该寄存器。如果向量IRQ请求,VIC将提供的最高优先级的请求的中断服务例程的地址,另外它提供一个默认的程序地址是由所有的非向量IRQ共享。默认的程序可以读取另一个VIC寄存器看看IRQ是否在工作。

6.5.1中断源

表4列出了每个外围功能的中断源。每个外围设备都有一个中断线连接到中断向量控制器,但可能有几个内部中断标志.个别中断标志也可以表示多个中断源。

表格 4 中断源

6.6引脚连接块

引脚连接块允许微控制器的选择引脚有一个以上的功能。配置寄存器控制的多路复用器允许引脚和芯片的外围设备之间的连接。外围设备应连接到相应的引脚被触发之前,并且在任何相关的中断优先级被启用前,对任何外围功能活动不映射到相关的引脚应考虑 。

6.7通用并行I/O(GPIO)和快速I/O

这是没有连接到一个特定的外围功能器件引脚的并行I/O寄存器控制,引脚可动态配置为输入或输出,同时单独的寄存器允许放置或清除任意数量的输出。寄存器的输出值可能回读,端口的当前状态也同样如此。

6.7.1特征

(1)位级设置和清除寄存器允许一个单一的指令集或清除任何数量的。

(2)个别位的方向控制。

(3)单独控制输出集和清除。

(4)所有I / O默认输入复位后。

6.7.2添加的功能寄存器组可在快速GPIO

(1)快速GPIO寄存器转移到尽可能最快的I / O臂局部总线时间,使端口引脚切换了3.5倍,比以前更快LPC2000系列设备。

(2)屏蔽寄存器允许处理端口位作为一组,留下其他位不变

(3)快速GPIO寄存器字节寻址

(4)整个端口值可以写在一个指令

(5)端口都可以通过任一旧系统寄存器组(GPIO)或本集团编制提供加速端口访问(快速GPIO)。

6.8 10位模数转换器

LPC2114 / 2124每个包含一个10位的逐次逼近模数转换器与四多路复用通道。

6.8.1特征

(1)测量范围为0 V至3 V

(2)能够执行超过400000个10位样本每秒。

(3)突发转换模式为单一或多个输入。

(4)对输入引脚或定时器匹配信号转换可选转换。

(5)每个模拟输入都有专门的结果寄存器以减少中断开销。

(6)每一个模拟输入可以生成一个中断,一旦转换完成。

6.8.2 LPC2114 / 2124 / 01的ADC功能

(1)每个模拟输入都有专门的结果寄存器以减少中断开销。

(2)每一个模拟输入可以生成一个中断,一旦转换完成。

(3)当数字I/O功能配置时,ADC是5V容限。

6.9 UART

LPC2114 / 2124每一个包含两个UART。除了标准的发送和接收数据的串口线,也提供了一个完整的调制解调器控制连接接口。

6.9.1特征

(1)16 B的接收和发送FIFO。

(2)登记地点符合16C550工业标准。

(3)接收机FIFO触发点在1 B,4 B,8 B,和14 B

(4)内置分数波特率发生器覆盖广泛的波特率没有需要特定值的外部晶体。

(5)传输FIFO控制使软件实现(XON / XOFF)UART对流量的控制。

(6)UART1配备标准的调制解调器接口信号。该模块还提供全面支持硬件流控制(自动CTS/RTS)。

6.9.2 LPC2114 / 2124 / 01中的UART功能

相比以前的LPC2000微控制器LPC2114 / 2124 / 01的UART介绍分数波特率发生器为UART,使这些微控制器实现标准波特率例如115200 BD与任何晶体频率超过2兆赫。此外,自动CTS/RTS流量控制功能完全由硬件实现。

bull;分数波特率发生器使标准波特率如115200 BD是实现与任何晶体频率以上2兆赫。

bull;自动波特率。

bull;自动CTS/RTS流量控制完全由硬件实现。

6.10 I2C总线串行I/O控制器

I2C总线是一个双向总线,其中IC控制只使用两条线:串行时钟线(SCL),和一个串行数据线(SDA)。每个设备是由一个唯一的地址识别,可以作为无论是一个只接收设备(如LCD驱动器或发射机与接收和发送信息的能力(如内存)。发射机和/或接收器可以工作在主或从模式,取决于芯片是否有启动数据传输或仅寻址。I2C总线是一个多主总线,它可以控制一个以上的总线主机连接到它。

LPC2114 / 2124实现I2C总线支持比特率为400 kbit/s(快速I2C总线)。 剩余内容已隐藏,支付完成后下载完整资料

资料编号:[137669],资料为PDF文档或Word文档,PDF文档可免费转换为Word

以上是毕业论文外文翻译,课题毕业论文、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。